OVERVIEW

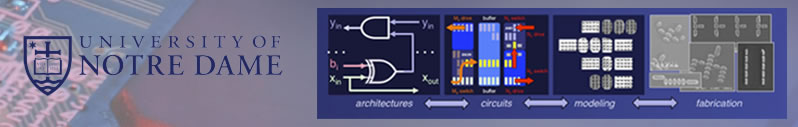

My research efforts have primarily targeted computational systems where magnetic elements with nanometer feature sizes are used to both process and store binary information. Why is this good? In conventional electronics, most computation is charge-based. A power supply maintains state, and thousands of electrons (each at ~40 kT) are needed to perform a single function. Alternatively, nanomagnet logic (NML) devices can process information in a cellular-automata like architecture, could dissipate < 40 kT per switching event for a gate operation, will retain state without power, and are intrinsically radiation hard. Thus, looking up to applications, NML has the potential to mitigate increasing chip-level power densities that are currently exacerbated by device scaling, could help to improve battery life in mobile information processing systems, and may operate in environments where transistor-based logic and memory cannot.

Sub-projects and Personnel

- (CMOS Compatible Clocking and Input/Output): My research is funded in part by the Semiconductor Research Corporation’s (SRC) Nanotechnology Research Initiative (NRI) under the umbrella of the Midwest Institute for Nanoelectronics Discovery (MIND). The NRI’s mission statement strongly suggests that emerging technologies be compatible with conventional transistor-based logic such that industry can leverage an existing, multi-billion dollar infrastructure, and ease the transition to new computational paradigms. As such, my research group has targeted CMOS-compatible “clocks” for controlling ensembles of NML devices, as well as the design and implementation of a magnetic-electrical interface for input and output.

- (Demonstration of the Five Fundamental Tenets for Digital Systems): For the last two years, I have pursued (for NML) the experimental demonstration of the five fundamental “tenets” [Waser 2003] that a device must satisfy if it is to be used to implement a digital system. In summary: (i) a device should have non-linear response characteristics, (ii) a device should enable a functionally complete logic set, (iii) power amplification (or gain) is needed, (iv) the output of one device must drive another (i.e. with no state variable change), and (v) dataflow directionality must be well defined. In line with my research philosophy, work at this level bolsters architectural-level research in more ways than one. First, it suggests that any candidate design will in fact be physically realizable. Second, it allows for the correlation of experimental data to physical-level simulations, which can further refine system-level performance projections.

- (Application Level Mappings): As work toward CMOS compatible clocking, I/O, and the experimental demonstration of the five fundamental tenets of digital systems progressed, I also conducted a parallel effort to extrapolate interconnect and gate performance to application-level structures (i.e. a 32-bit adder) to ensure that the potential for performance wins at this level always remained given the specific structures being built. Now, given the establishment of a sound experimental foundation, in addition to low-power, general-purpose logic, more specific, system-level architectures and applications will receive additional focus. Particular attention is being given to how the clock dictates dataflow in an NML circuit, and the intrinsic properties of the technology itself. All design efforts associated with this effort are constrained by realistic manufacturing (CMOS) process flows, and are guided by parallel experimental efforts.

Alumni

- Katie Butler

- Himadri Dey

- Aaron Dingler

- Steven Kurtz

- Peng (Andy) Li

- Shiliang (Shawn) Liu

- Indranil Palit

- Faisal Shah

- M. Jafar Siddiq

- Edit Varga

- M. Tanvir Alam — Currently a Post-doctoral Researcher with Jeff Bokor at U.C. Berkeley.

- Michael Crocker — Currently an Assistant Professor at Pacific Lutheran University

Support

- SRC NRI via the Midwest Institute for Nanoelectronics Discovery, $2,220,986

- DARPA via “Nanomagnet Logic,” $4,279,367

- ONR via “Radiation-Hard Nanomagnet Logic with Electronic Input and Output,” $482,671

- The National Science Foundation via “MRI: Acquisition: Characterization of and I/O for Magnetic Logic Structures,” $658,070 (ended)

- The National Science Foundation via “Applications, Architectures, and Circuit Design for Nanoscale Magnetic Logic Devices,” $300,000 (ended)

- DOD via “Blending Processing into Advanced Memory Technologies to Enhance Massive, Memory-critical Applications,” $980,153 (ended)