University of Notre Dame, Department of Computer Science & Engineering

#### CSE 30321 - Lecture 28 - Introduction to Parallel Processing

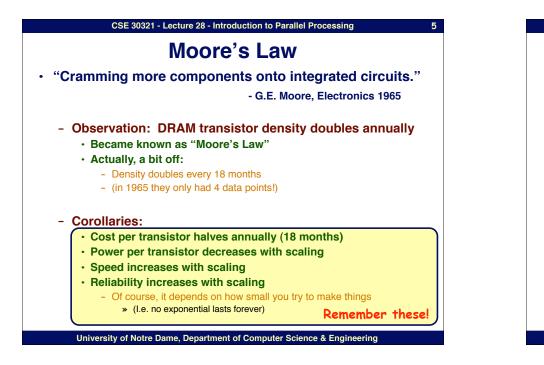

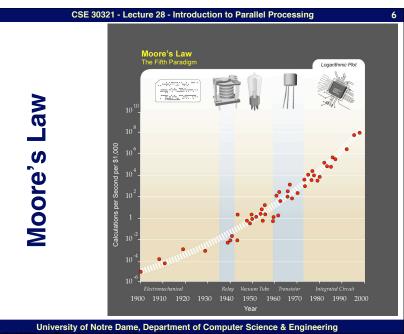

# Moore's Law

- Moore's Curve is a self-fulfilling prophecy

- 2X every 2 years means ~3% per month

- I.e. ((1 X 1.03) \* 1.03)\*1.03... 24 times = ~2

- Can use 3% per month to judge performance features

- If feature adds 9 months to schedule...it should add at least 30% to performance

- (1.03<sup>9</sup> = 1.30 ⇒ 30%)

#### CSE 30321 - Lecture 28 - Introduction to Parallel Processing

### A bit on device performance...

- One way to think about switching time:

- Charge is carried by electrons

- Carrier velocity is proportional to the lateral E-field between source and drain

- i.e. v = mE

- m = carrier mobility (and can be though of as a constant)

- Electric field defined as: E = V<sub>ds</sub>/L

- Time for charge to cross channel = length/speed

- (i.e. meters / (meters/s) = seconds)

- = L/v

- = L/(mE)

- =  $L/(m^*(V_{ds}/L))$

- = L<sup>2</sup>/(mV<sub>ds</sub>)

Thus, to make a device faster, we want to either increase  $V_{ds}$  or decrease feature sizes (i.e. L)

# Some more important relationships

- What about power (i.e. heat)?

- First, need to quickly discuss equation for capacitance:

- $C_L = (e_{ox}WL)/d$

- e<sub>ox</sub> = dielectric, WL = parallel plate area, d = distance between gate and substrate

- Then, dynamic power becomes:

- $P_{dyn} = C_L V_{dd}^2 f_{0-1}$

- Dynamic power is a function of the frequency of 0 to 1 or 1 to 0 transitions (as this involves the movement of charge)

- » Note frequency in this context is NOT clock frequency

- Note that as W and L scale,  $C_{\text{L}}$  decreases which in turn will cause a decrease in  $\mathsf{P}_{dyn}.$

- Note that while an increase in  $V_{dd}$  will \*decrease\* switching time, it will also cause a quadratic \*increase\* in dynamic power.

University of Notre Dame, Department of Computer Science & Engineering

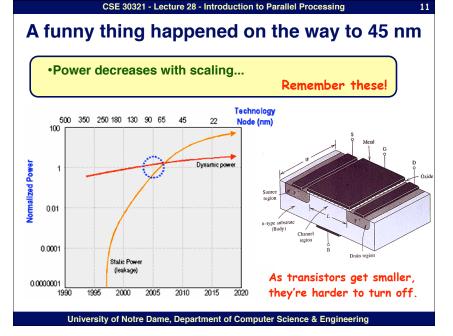

### A funny thing happened on the way to 45 nm

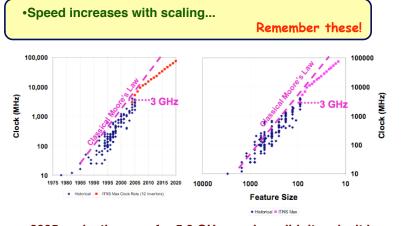

2005 projection was for 5.2 GHz - and we didn't make it in production. Further, we're still stuck at 3+ GHz in production.

University of Notre Dame, Department of Computer Science & Engineering

#### CSE 30321 - Lecture 28 - Introduction to Parallel Processing

**Remember these**!

#### A funny thing happened on the way to 45 nm

- Speed increases with scaling...

- Power decreases with scaling...

#### Why the clock flattening? POWER!!!!

University of Notre Dame, Department of Computer Science & Engineering

Other reasons too, but this should give you a good feel for technology...

University of Notre Dame, Department of Computer Science & Engineering

- Disk (magnetic): density +25%, speed +4%

University of Notre Dame, Department of Computer Science & Engineering

University of Notre Dame, Department of Computer Science & Engineering