Computing at the Nanoscale

CSE 40547 / 60547

246 Debartolo Hall

Monday-Wednesday 9:10 a.m. - 10:25 a.m.

Course Objectives

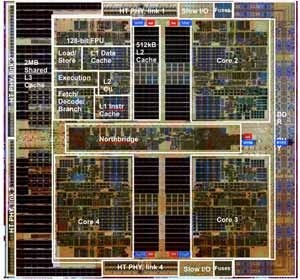

In Computing at the Nanoscale, we will investigate what computer architectures and new applications emerging technologies might enable. We will begin by addressing challenges to current CMOS scaling (at both the device and architectural levels) and consider how an end to Moore's Law might impact application-level performance and (b) what industry is doing to "extend CMOS" and continue the performance scaling trends that we have come to expect for the last 30+ years beyond the year 2020. (Techniques such as 3D integration will be introduced and their architectural impact will be assessed.) We will then look at how new devices (i.e. emerging technologies) might help us to improve the performance of future computational systems as well as what new applications might be enabled with new devices. In class, we will discuss not only how a new device works, but also how new ways of representing 1s and 0s will ultimately affect systems-level structures.

Course Schedule

| Day | Date | Topic | Assignment Out | Assignment In | Useful References | |

|---|---|---|---|---|---|---|

| 1 | W | Jan. 14 |

Discuss scope of class, student interests, syallbus Syllabus The State of State |

SRC Paper Review Assignment 01 |

||

| 2 | M | Jan. 19 |

Transistor-based computing and historical scaling Slides (Part 1) Slides (Part 2) |

|||

| 3 | W | Jan. 21 |

Transistor-based computing and historical scaling Slides |

Assignment 01 | "Leakage Current: Moore's Law Meets Static Power" Kim, et. al. | |

| 4 | M | Jan. 26 |

Roadblocks to transistor-based computing Slides |

David Frank Lecture Assignment 02 (see document links) |

||

| 5 | W | Jan. 28 |

CMOS-based Probabilistic CMOS |

“Probabilistic Arithmetic and Energy Efficient Embedded Signal Processing” Palem, et. al. | ||

| 6 | M | Feb. 2 | Subthreshold Probabilistic CMOS | Assignment 02 |

Discuss:

Nanoscale Logic based on MRFs” by Bahar, et. al. Other paper references: Bahar, et. al. (DATE ’06) Bahar, et. al. (DAC ’05) Bahar, et. al. (ICCAD ’03) Yedidia (Belief Propagation) |

|

| 7 | W | Feb. 4 | Scaling's Impact on High Performance Architecture | Slides: (von Neumann), (superscalar, multicore), (technology), (reconfigurable), (neural networks) |

||

| 8 | M | Feb. 9 | I/O issues with High Performance Architecture | (Slides Forthcoming) | ||

| 9 | W | Feb. 11 | 3D Integration |

Loh, et. al. (MICRO '07) Brockman, et. al. (ISCA '08) |

||

| 10 | M | Feb. 16 | CNT FETs + Interconnect | Assignment 03 |

Avouris, Scientific American “Nanotubes for Electronics” Avouris, J. Vac. Sci. Tech. B. “Transistor structures … in CNTs” Banerjee, ICCAD ‘05 “Perf. Analysis Of CNT IC for VLSI Apps.” Banerjee, DAC ‘06 “Are CNTs Future of VLSI Interconnects?” |

|

| 11 | W | Feb. 18 | FINFETs | |||

| 12 | M | Feb. 23 | TFETs | |||

| 13 | W | Feb. 25 | Teramac |

Heath, et. al., Science "A Defect-Tolerant Computer Architecture..." |

||

| 14 | W | Mar. 2 | Nanowire-based circuits (1) |

Dehon, JETC, 1(2), 2005 “Nanowire-Based Programmable Architectures” Lieber, Nano Letters, 3(7) “Nanolithography Using Hierarchically Assembled Nanowire Masks” Lieber, Science, 291, 2001 "Directed Assembly of One-Dimensional Nanostructures into Functional NWs” Heath, ChemPhysChem, (3), 2002 “2D Molecular Electronic Circuits” |

||

| 15 | Mar. 4 | Nanowire-based circuits (2) | ||||

| 16 | W | Mar. 17 | Nanowire-based circuits (3) | Reconfigurable Logic with Nanowires Assignment 04 | ||

| 17 | M | Mar. 23 | CMOL (1) |

Strukov, Nanotechnology (16), 2005 “CMOL FPGA: ...” Strukov, Nanotechnology, (16), 2005 “Prospects for Tera-bit Scale Nanoelectronic Memories” |

||

| 18 | W | Mar. 25 | CNOL + FPNI | PLAs vs. CMOL vs. FPNI Assignment 05 |

Snider, Nanotechnology, (18), 2007 “...Field Programmable Nanowire Interconnect” |

|

| 19 | M | Mar. 30 | Alternate State Variables (Magnetics) | (No links) | ||

| 20 | W | Apr. 1 | QCA (emphasis on magnetic) | Reminder Proj. 5 due on 4/3 Final Project |

Imre, Science, 311(5758) "Majority Logic Gate for MQCA" Niemier, ISLPED, 2007 “Clocking Structures ... for Nanomagnet Logic” |

|

| 21 | M | Apr. 6 | Nano Electromechanical Switches |

Rueckes, Science, 289(5476) "Carbon Nanotube-based Nonvolatile Random Access Memory for Molecular Computing" Zhou, ISLPED, 2007 “Low Power FPGA Design Using Hybrid CMOS-NEMS Approach” Banerjee, DAC, 2007 “Design and Analysis of Hybrid NEMS-CMOS Circuits for Ultra Low-Power Applications” Jha, DAC, 2007 “NanoMap: An Integrated Design Optimization Flow for a Hybrid nanotube/CMOS Dynamically Reconfigurable Architecture” |

||

| 22 | W | Apr. 8 | Memory (The Incumbents) |

Galatsis, IEEE Circuits and Devices, May/June 2006, p. 12-21 “Emerging Memory Devices” Brewer, IEEE Circuits and Devices, March/April 2005, p. 13-20 “Memory Technology for the Post CMOS Era” |

||

| 23 | W | Apr. 15 | Memory (The Challengers) (1) |

2007 Nobel Prize Notes “The Discovery of Giant Magnetoresistance” Cockburn “Tutorial on Magnetic Tunnel Junction Magnetoresistive Random-Access Memory” Gallagher, IBM J. Res.Dev. 50(1) “Development of the Magnetic Tunnel Junction MRAM at IBM... Nam “Switching Properties in Spin Transfer Torque MRAM with sub-50 nm MTJ Size” |

||

| 24 | F | Apr. 17 | Memory (The Challengers) (2) |

Memory Assignment 06 |

See Lecture 23 | |

| 25 | M | Apr. 20 | CNNs (1) | TBD | ||

| 26 | W | Apr. 22 | CNNs (2) | Assignment | Snider Paper | |

| 27 | M | Apr. 27 | Catch up + Quantum Computing | TBD | ||

| 28 | W | Apr. 29 | Quantum Computing | Final Project due Friday of Finals Week |

Contact Information

Instructor

-

Michael T. Niemier(mniemier@nd.edu)

380 Fitzpatrick Hall

Notre Dame, IN 46556

(574) 631-3858

Office Hours: Stop by any time.