### **CSE30321 Computer Architecture I**

Lab 1: Reviews – Verilog, Xlilinx, Etc. (50 points)

Assigned: Week of September 1st. Due: Week of September 8th

# 1 Big Picture Introduction

"Why do I have spend additional time outside of class working in the lab?" or alternatively "What am I possibly going to get out of the lab that I can't learn in class?"

Over the course of the semester, you'll be working to complete labs outside of class. Before getting started with Lab 01, I'll try to briefly explain what the lab sessions are designed to do. In short, computer architecture is a course about designing microprocessors. In lab, you'll have the opportunity to apply ideas learned in class to expand the functionality or improve the performance of some real processor design. Moreover, you'll actually use some of the same software and hardware design tools that someone working for a company that designs and builds microprocessors might leverage.

As an example, it certainly is important to weigh both the pros and cons of adding a new instruction to some computer architecture. While the new instruction might make the processor more functional, it might also make it harder to implement too. While the first step in this decision making process might be done "on paper" – and involve thinking about how the new instruction might affect the complexity of your control logic, whether or not you'll need to build a bigger multiplexer, etc. – more detailed simulations are also necessary to make sure the improvement performs equally well once it is actually fabricated "on chip".

In real life your idea that exists "on paper" would have a life cycle that might look something like this:

- The new instruction would probably next be simulated at the behavioral level (where you figure out what new control signals might be needed, you check the changes that are made to finite state machine associated with your control logic, etc.)

- 2. The behavioral model might be synthesized to create a logic gate representation of the hardware that's actually needed to implement the design.

- 3. You would interact with compiler writers to make sure that the new instruction actually helps improve the performance of programming constructs that are commonly used.

- 4. The logic gate representation might be processed further to get to a representation of the design that could be sent to a fabrication facility and physically built.

We won't talk much about items 3 and 4 above in this class. (You'd discuss work associated with item 3 in Compilers in the Fall of 2010 and you'd discuss work with item 4 in VLSI Design in the Fall of 2010.) However, in the labs this semester, you *will* get hands on experience with items 1 and 2 – which will help prepare you for future courses that you might take.

#### There's a "practical" nature to the labs too ...

At the end of the semester, you'll be asked to apply the knowledge you've learned in class to make some performance improvements to a simple processor design. You might look at ways to improve performance, lower the implementation costs, etc. The only practical way to manage a design of even this complexity is to use the tools that you'll learn about over the course of the semester in the labs. With this end goal in mind, each lab has been designed to introduce you to different aspects of processor design – so you'll have prior knowledge of all of the design techniques that you'll need to leverage in you're final project.

# 2 Objectives for this Lab

The goals of this lab are essentially two fold:

- The lab is designed to introduce and review the tools that you'll use in lab over the course of the entire fall semester. More specifically, we'll review the Verilog concepts learned in CSE 20221 that you'll need to apply in lab assignments in CSE 30321. You'll also become familiar with the ModelSim simulation tool.

- 2. You'll also learn how to use Verilog to design a finite state machine. (Recall from Lecture 03 that finite state machines can be quite useful in designing and implementing the control signals necessary for a given instruction.)

### 3 Lab 01 Procedures

- Recall the assignment from CSE20221 in which the FPGA interfaced with a PS/2 keyboard (link on course web page). Begin by creating a directory and downloading the completed Verilog code and schematic for the CSE20221 assignment (link to zip files on course web page). Open Xilinx ISE and create a new project for this lab ("File->New Project"). Add the sources you just downloaded to the project ("Project->Add Copy of Source...").

- 2. Design a finite state machine in Verilog to recognize a 4 character stream input from the keyboard. The input stream to recognize is "GOND". The characters in the input stream can be repeated and should still be recognized, i.e. something like "GGGOONNNNDD" is valid input. Create a Verilog module for the FSM (and any other modules you think you might need) in Xilinx ISE as part of the keyboard project. The input to the module will be the output from "shiftreg11" (i.e. kbd data[10:0]). The state machine will determine if the input matches the desired string. An output signal should go high when "GOND" is recognized, and a different output signal should go high while "GOND" has not been recognized.

- Note: You will not need the clock divider, digit multiplexer, or seven segment decoder from the CSE20221 lab as we will not be downloading to the boards. Instead, you will simulate input to the shift register, which will be shifted out to your finite state machine and generate output signals accordingly.

- 4. Simulate and debug your design using ModelSim. Create a testbench waveform that will go through 3 inputs that do not match, followed by "GOND". The Basys reference manual lists the hexadecimal code for each key you can ignore the "key up" codes specified in the manual, i.e. only recognize the 4 key-code for "GOND". ModelSim should be selected as the default simulator. If the ISE simulator opens instead, double-click the device (xc3s100e-5vq100) in the "Sources" tab, and in the window that opens select "ModelSim XE" as the default simulator.

- 5. When ModelSim opens, you will be presented with a command prompt, a waveform display, and a list of signals from the ISE testbench. The simulation should already have run for the default 1000ns that the ISE testbench specifies. Note that you may have to right click the waveform and click "Zoom full" to see the results (sometimes it starts zoomed in or out). To run for a longer time, just type "run Xns" at the command prompt, where X is the desired time in nanoseconds. Print out parts of the waveform that demonstrate correct functionality of your design.

- 6. Note: In previous years we have had troubles with the ModelSim Licenses. Before running ModelSim, run the License Wizard (Start->Programs->ModelSim...) twice. If after doing this ModelSim gives errors about the license contact the lab TA and tell him what machine you were using, and try using ModelSim on a different machine. If all fails, you can use the built-in ISE simulator.

### 4 What to Turn In

- Prepare a typed report that includes a printout of the waveform used to verify your design and a description

of how the waveform demonstrates correct functionality. Your report will be graded for its technical content

as well as its style and grammar.

- Answer the following questions:

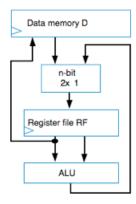

Figure 1: 3-instruction processor datapath.

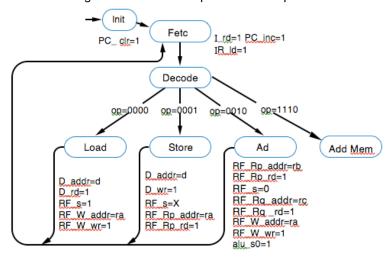

Figure 2: Finite state machine to revise.

- In this question, we're going to work with the initial datapath for the 3-instruction processor (shown below). Let's assume that we want to modify this datapath to add an instruction that performs an ALU operation on any two memory locations and stores the result in a register file location. Add the necessary components to Fig. 1 to make this possible.

- 2. Using the new datapath you've designed, write out the machine instructions for performing the operation d(4) = d(5) + d(6) + d(7).

- 3. Trace the sequence of instructions through the datapath.

- 4. For comparison, write out the sequence of instructions to perform d(4) = d(5)+ d(6) + d(7) using the original, un-enhanced datapath. (Foreshadowing: Do you think the new instruction helps? How would you quantify your answer?)

- Finally, update the finite state machine to support this new ALU instruction. For reference, the FSM for the 3-instruction processor for the original datapath is shown in Fig. 2. You probably want to refer to your answer for Part 1.

- (Note I expect a report of about 1 to 1.5 pages that looks something like the first page of this lab handout.)

## 5 Useful References

• Frank Vahid's Digital Design (Ch. 9)

- CSE20221 Handouts on Verilog (links on course web page)

- ModelSim and Verilog tutorial videos (link on course web page)