**Lecture 01**

**Introduction to CSE 30321**

#### Huh?

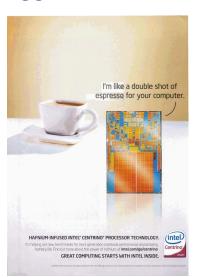

All of the following are magazines that are regularly delivered to the Niemier household.

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

You can learn about good routes to run if you're visiting Chicago...

**University of Notre Dame**

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

#### You can learn about the best ice cream...

# You can read about Pat Robertson and Al Sharpton advocating ways to reduce the effects of global climate change!

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

7

## And if you're looking to buy a computer, Intel suggests their dual core Centrino chip...

As you might guess, this brings us to CSE 30321!

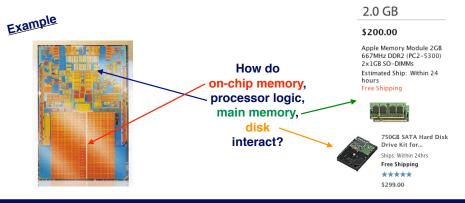

This is essentially a picture of one of Intel's computer architectures...

We'll learn about how different parts of a processor are organized and work together

If you're in the market for a wide-body jet, Boeing has just the thing...

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

8

#### So, what are the goals of this course?

- At the end of the semester, you should be able to...

- ...describe the fundamental components required in a single core of a modern microprocessor

- (Also, explain how they interact with each other, with main memory, and with external storage media...)

**University of Notre Dame**

#### So, what are the goals of this course?

- At the end of the semester, you should be able to...

- ...compare and contrast different computer architectures to determine which one performs better...

| Processor<br>Number <sup>1</sup> | Architecture | Cache  | Clock<br>Speed | Front<br>Side<br>Bus | Dual-core | Enhanced<br>Intel<br>SpeedStep®<br>Technology² | Execute<br>Disable Bit <sup>o</sup> | Inte<br>64 |

|----------------------------------|--------------|--------|----------------|----------------------|-----------|------------------------------------------------|-------------------------------------|------------|

| E2220                            | 65 nm        | 1MB L2 | 2.40 GHz       | 800 MHz              | 1         | /                                              | 1                                   | /          |

| E2200                            | 65 nm        | 1MB L2 | 2 20 GH        | 800 MHz              | 1         | /                                              | 1                                   | /          |

| E2180                            | 65 nm        | 1MB L2 | 2.00 GHz       | 800 MHz              | 1         | /                                              | 1                                   | 1          |

| E2160                            | 65 nm        | 1MB L2 | 1.80 GHz       | 800 MHz              | 1         | /                                              | ✓                                   | 1          |

| E2140                            | 65 nm        | 1MB L2 | 1.60 GHz       | 800 MHz              | 1         | 1                                              | /                                   | 1          |

| T2330                            | 65 nm        | 1MB L2 | 1.60 GHz       | 533 MHz              | 1         | /                                              | ✓                                   | /          |

| T2310                            | 65 nm        | 1MB L2 | 1.46 GHz       | 533 MHz              | 1         | 1                                              | ✓                                   | 1          |

| T2130                            | 65 nm        | 1MB L2 | 1.86 GHz       | 533 MHz              | 1         | /                                              | ✓                                   |            |

| T2080                            | 65 nm        | 1MB L2 | 1.73 GHz       | 533 MHz              | 1         | /                                              | 1                                   |            |

| T2060                            | 65 nm        | 1MB L2 |                | 533 MHz              | 1         | /                                              | 1                                   |            |

| T2370                            | 65 nm        | 1MB L2 | 1.73 GHz       | 533 MHz              | /         | /                                              | /                                   | /          |

If you want to do X, which processor is best?

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

#### So, what are the goals of this course?

- At the end of the semester, you should be able to...

- ...understand how code written in a high-level language (e.g. C) is eventually executed on-chip...

#### Example

#### In C:

```

void insertionSort(int numbers[], int array_size)

int i, j, index;

for (i=1; i < array_size; i++)</pre>

index = numbers[i];

while ((j > 0) && (numbers[j-1] > index))

numbers[j] = numbers[j-1];

j = j - 1;

numbers[j] = index;

```

```

public static void insertionSort(int[] list, int length) {

int firstOutOfOrder, location, temp;

for(firstOutOfOrder = 1; firstOutOfOrder < length; firstOutOfOrder++) {

if(list[firstOutOfOrder] < list[firstOutOfOrder - 1]) {

temp = list[firstOutOfOrder]:

location = firstOutOfOrder:

list[location] = list[location-1];

location--:

while (location > 0 && list[location-1] > temp);

list[location] = temp;

```

Both programs could be run on the same processor... how does this happen?

**University of Notre Dame**

#### So, what are the goals of this course?

- At the end of the semester, you should be able to...

- ...design a processor architecture to meet a specific performance target...

You might choose to add more or less on-chip memory...

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

#### A tangent...

- We'll talk about 2 more course goals in a little bit, but right now, I'd like to ask the class a few questions...

- Question 1:

- How many people are EE, CPEG, CS, other?

- Question 2:

- By major, does anyone have any definitive thoughts about what they want to do after graduation?

- Question 3:

- Preface: last slide talked about SW...

- How many people are more interested in the SW side of CSE than the HW side of CSE?

- Question 4:

- How many people view CSE 30321 as more a "HW course"

- How many people think other more "SW oriented" courses are more relevant for their major?

#### Let's digress...

- I asked the questions on the last slide not just to gauge interest, but to bring up an important point...

- For last 20 years, if interested in SW, computer architecture was probably *not* the most important class for you.

- But...changes in technology are having a profound impact on conventional/established computer architectures

- We're presently at the very beginning of this storm...

- We'll need significant engagement from programmers to continue the processor performance scaling trends of the last 40 years...

- ... this will impact your career...

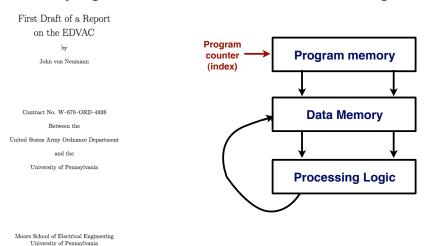

June 30, 1945

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

### A little history... programs

Stored program model has been around for a long time...

**University of Notre Dame**

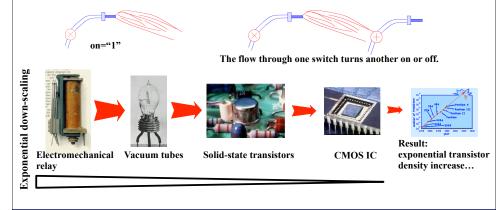

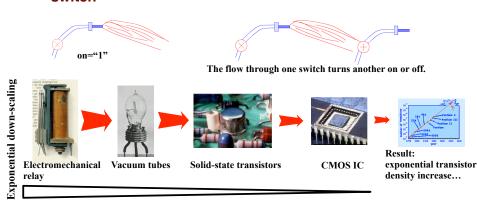

#### A little history... Zuse's paradigm

- Konrad Zuse (1938) Z3 machine

- Use binary numbers to encode information

- Represent binary digits as on/off state of a current switch

University of Notre Dame, Department of Computer Science & Engineering

CSE 30321 - Lecture 01 - Introduction to CSE 30321

Represent binary digits as on/off state of a current switch

#### Transistors used to manipulate/store 1s & 0s

**Switch-level representation**

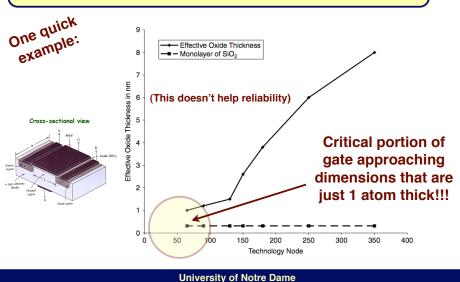

#### **Cross-sectional view**

Using above diagrams as context, note that (with NMOS) if we (i) apply a suitable voltage to the gate & (ii) then apply a suitable voltage between source and drain, current will flow.

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

**University of Notre Dame**

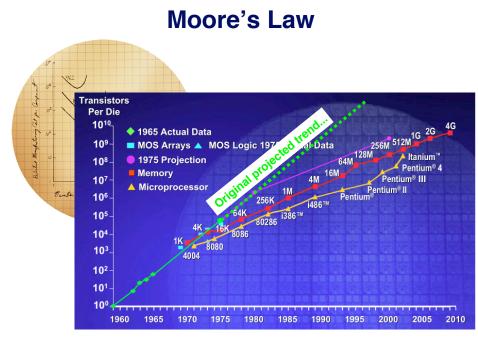

#### Moore's Law

"Cramming more components onto integrated circuits."

- G.E. Moore. Electronics 1965

- Observation: DRAM transistor density doubles annually

- · Became known as "Moore's Law"

- Actually, a bit off:

- Density doubles every 18 months (now more like 24)

- (in 1965 they only had 4 data points!)

- Corollaries:

- Cost per transistor halves annually (18 months)

- · Power per transistor decreases with scaling

- · Speed increases with scaling

- · Reliability increases with scaling

- Of course, it depends on how small you try to make things

- » (I.e. no exponential lasts forever)

Remember these!

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

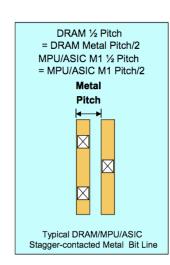

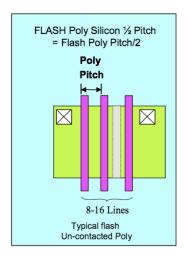

#### Feature sizes...

Figure 2 2005 Definition of Pitches

#### Moore's Law

- Moore's Curve is a self-fulfilling prophecy

- · 2X every 2 years means ~3% per month

- I.e.  $((1 \times 1.03) \times 1.03) \times 1.03 \times 1.03 \times 24 \times 1.03 \times 1$

- Can use 3% per month to judge performance features

- If feature adds 9 months to schedule...it should add at least 30% to performance

- (1.039 = 1.30  $\Rightarrow$  30%)

#### **University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

#### 00E 000E1 Ecolule 01 IIII 0ddciloii to 00E 000E1

#### Some more important relationships

- What about power (i.e. heat)?

- First, need to quickly discuss equation for capacitance:

- $C_L = (e_{ox}WL)/d$

- e<sub>ox</sub> = dielectric, WL = parallel plate area, d = distance between gate and substrate

- Then, <u>dynamic</u> power becomes:

- $P_{dyn} = C_L V_{dd}^2 f_{0-1}$

- Dynamic power is a function of the frequency of 0 to 1 or 1 to 0 transitions (as this involves the movement of charge)

- » Note frequency in this context is NOT clock frequency

- Note that as W and L scale,  $C_L$  decreases which in turn will cause a decrease in  $P_{dvn}$ .

- Note that while an increase in V<sub>dd</sub> will \*decrease\* switching time, it will also cause a quadratic \*increase\* in dynamic power.

#### A bit on device performance...

- One way to think about switching time:

- Charge is carried by electrons

- Carrier velocity is proportional to the lateral E-field between source and drain

- i.e. v = mE

- m = carrier mobility (and can be though of as a constant)

- Electric field defined as: E = V<sub>ds</sub>/L

- Time for charge to cross channel = length/speed

- (i.e. meters / (meters/s) = seconds)

- $\cdot = L/v$

- $\cdot = L/(mE)$

- $\cdot = L/(m^*(V_{ds}/L))$

- = L<sup>2</sup>/(mV<sub>ds</sub>)

Thus, to make a device faster, we want to either increase V<sub>ds</sub> or decrease feature sizes (i.e. L)

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

2

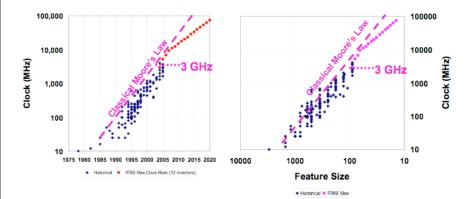

#### A funny thing happened on the way to 45 nm

Speed increases with scaling...

Remember these!

2005 projection was for 5.2 GHz - and we didn't make it in production. Further, we're still stuck at 3+ GHz in production.

**University of Notre Dame**

A funny thing happened on the way to 45 nm

350 250 180 130 90 65

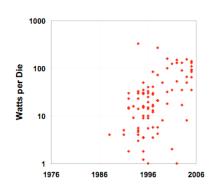

Power decreases with scaling...

**dormalized Power**

0.0001

0.0000001

Remember these!

Technology

Node (nm)

Dynamic power

2015

CSE 30321 - Lecture 01 - Introduction to CSE 30321

#### A funny thing happened on the way to 45 nm

- Speed increases with scaling...

- · Power decreases with scaling...

Remember these!

#### Why the clock flattening? POWER!!!!

**University of Notre Dame**

CSE 30321 - Lecture 01 - Introduction to CSE 30321

0

Static Power

2000

2005

**University of Notre Dame**

2010

•Reliability increases with scaling... Remember these!

Other reasons too, but this should give you a good feel for technology...

University of Notre Dame, Department of Computer Science & Engineering

#### Transistors used for memory too...

Saw earlier, that transistors used for *on chip* memory too... Problem: Program, data = bigger + power problem isn't going away...

- Why? Put faster memory closer to processing logic...

- SRAM (logic): density +25%, speed +20%

- DRAM (memory): density +60%, speed +4%

- Disk (magnetic): density +25%, speed +4%

University of Notre Dame, Department of Computer Science & Engineering

CSE 30321 - Lecture 01 - Introduction to CSE 30321

31

#### This idea has been extended...

Quad core chips...

7, 8, and 9 core chips...

Practical problems must be addressed!

Advances in parallel programming are necessary! (We'll get into later in the semester)

University of Notre Dame, Department of Computer Science & Engineering

#### Solution?

Motivation:

Processor complexity is good enough,

transistor sizes scale,

we can slow processors down,

manage power, and get performance from...

#### **Parallelism**

Top 5 Must-Haves

POWERFUL PROCESSOR

A portrait of performance. "My generative portraits are demanding on the processors in my laptop, as they continuously manipulate video," says Lincoln. Thankfully, the dual-core performance of Intel Centrino processor technology can handle intensive tasks with flying colors.

(i.e. 1 processor, 1 ns clock cycle vs. 2 processors, 2 ns clock cycle)

University of Notre Dame, Department of Computer Science & Engineering

CSE 30321 - Lecture 01 - Introduction to CSE 30321

- 3

#### So, what are the goals of this course?

- At the end of the semester, you should be able to...

- ...explain and articulate why modern microprocessors now have more than 1 core...

- Why?

- For 8, 16 core chips to be practical, we have to be able to use them

- Students in this class should go on to play a role in making such chips useful...

#### So, what are the goals of this course?

- · At the end of the semester, you should be able to...

- Apply fundamental knowledge about single core machines, dual core machines, performance metrics, etc. to design a microprocessor such that it (a) meets a target set of performance goals and (b) is realistically implementable.

Now, let's look at the syllabus

**University of Notre Dame**