# Lecture 22 Cache Examples

## Lecture 22 - Cache Examples

## Lecture 22 - Cache Examples

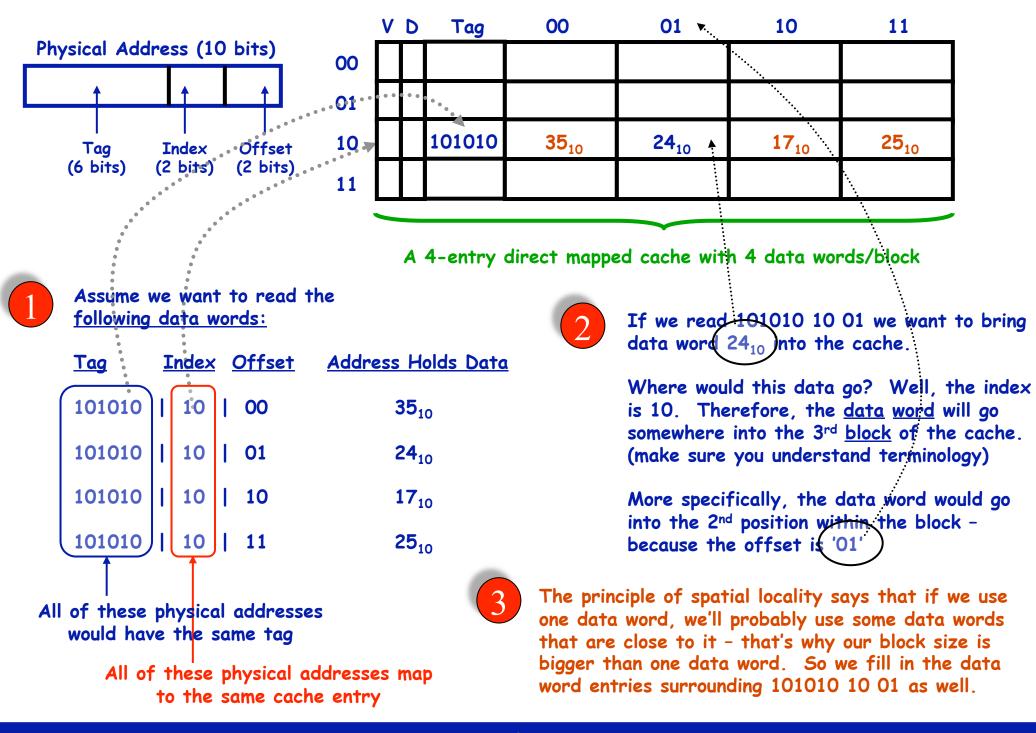

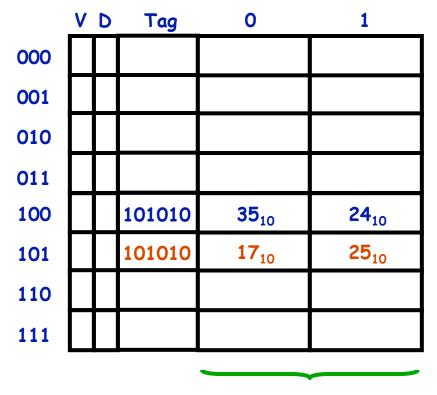

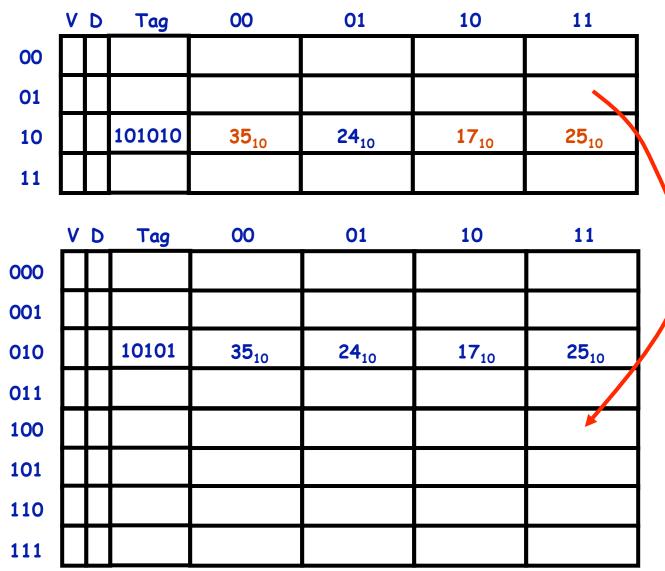

V D Tag 00 01 10 11 00 01 **24**<sub>10</sub> **17**<sub>10</sub> **25**<sub>10</sub> 101010 ..**▼ 35**<sub>10</sub> 10 4 11

A 4-entry direct mapped cache with 4 data words/block

Therefore, if we get this pattern of accesses when we start a new program:

What happens if we get an access to location: 100011 | 10 | 11 (holding data: 12<sub>10</sub>)

1.)101010 10 002.)101010 10 013.)101010 10 10

4.) 101010 10 11

After we do the read for 101010 10 00 (word #1), we will automatically get the data for words #2, 3 and 4.

What does this mean? Accesses (2), (3), and (4) ARE NOT <u>COMPULSORY</u> <u>MISSES</u>

Index bits tell us we need to look at cache block 10.

So, we need to compare the <u>tag</u> of this address – 100011 – to the tag that associated with the current entry in the cache block – 101010

These DO NOT match. Therefore, the data associated with address 100011 10 11 IS NOT VALID. What we have here could be:

- A <u>compulsory miss</u>

- (if this is the 1<sup>st</sup> time the data was accessed)

- A conflict miss:

- (if the data for address 100011 10 11 was present, but kicked out by 101010 10 00 - for example)

## Lecture 22 - Cache Examples

This cache can hold 16 data words...

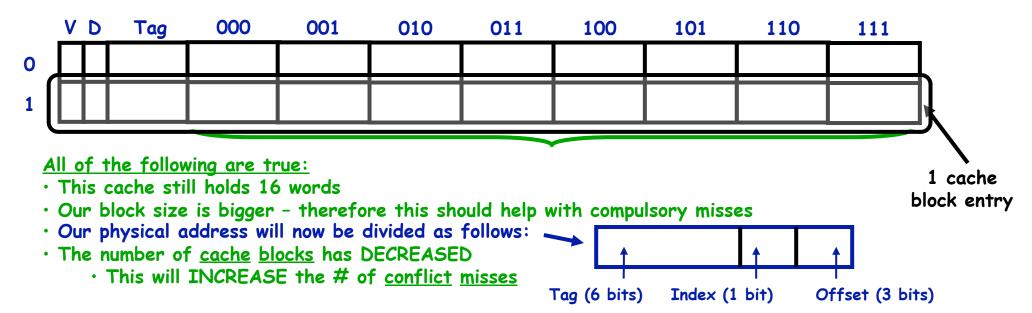

What if we change the way our cache is laid out – but so that it still has 16 data words? One way we could do this would be as follows:

What if we get the same pattern of accesses we had before?

Pattern of accesses: (note different # of bits for offset and index now)

Note that there is now more data associated with a given cache block.

- 101010 1 000 1.) 101010 1 001 2.)

- 3.) 101010 1 010 101010 1 011

- 4.)

However, now we have only 1 bit of index. Therefore, any address that comes along that has a tag that is different than '101010' and has 1 in the index position is going to result in a conflict miss.

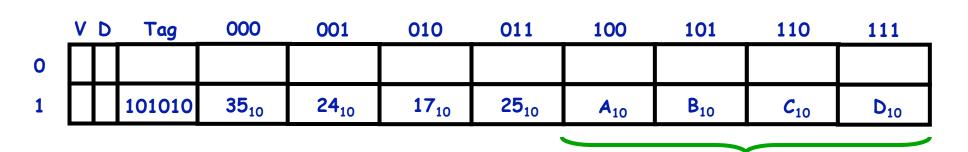

But, we could also make our cache look like this...

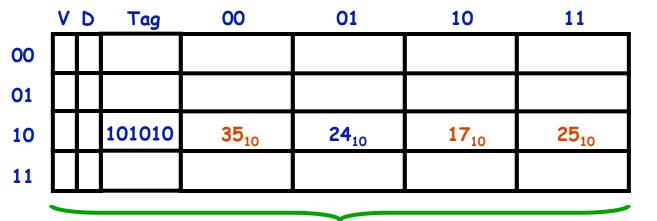

There are now just 2 words associated with each cache block. Again, let's assume we want to read the <u>following data words:</u>

| Tag                                                                    |     |   | Address Holds Data      |

|------------------------------------------------------------------------|-----|---|-------------------------|

| 1.) 101010                                                             | 100 | 0 | <b>35</b> 10            |

| 2.) 101010                                                             | 100 | 1 | <b>24</b> <sub>10</sub> |

| 3.) 101010                                                             | 101 | 0 | <b>17</b> <sub>10</sub> |

| <ol> <li>2.) 101010</li> <li>3.) 101010</li> <li>4.) 101010</li> </ol> |     | 1 | <b>25</b> <sub>10</sub> |

Assuming that all of these accesses were occurring for the  $1^{st}$  time (and would occur sequentially), accesses (1) and (3) would result in <u>compulsory</u> <u>misses</u>, and accesses would result in hits because of <u>spatial locality</u>. (The final state of the cache is shown after all 4 memory accesses).

Note that by organizing a cache in this way, <u>conflict</u> <u>misses</u> will be reduced. There are now more addresses in the cache that the 10-bit physical address can map too.

Lecture 22 - Cache Examples

But what about capacity misses?

## What's a <u>capacity miss</u>?

- The cache is only so big. We won't be able to store every block accessed in a program must them swap out!

- Can avoid capacity misses by making cache bigger

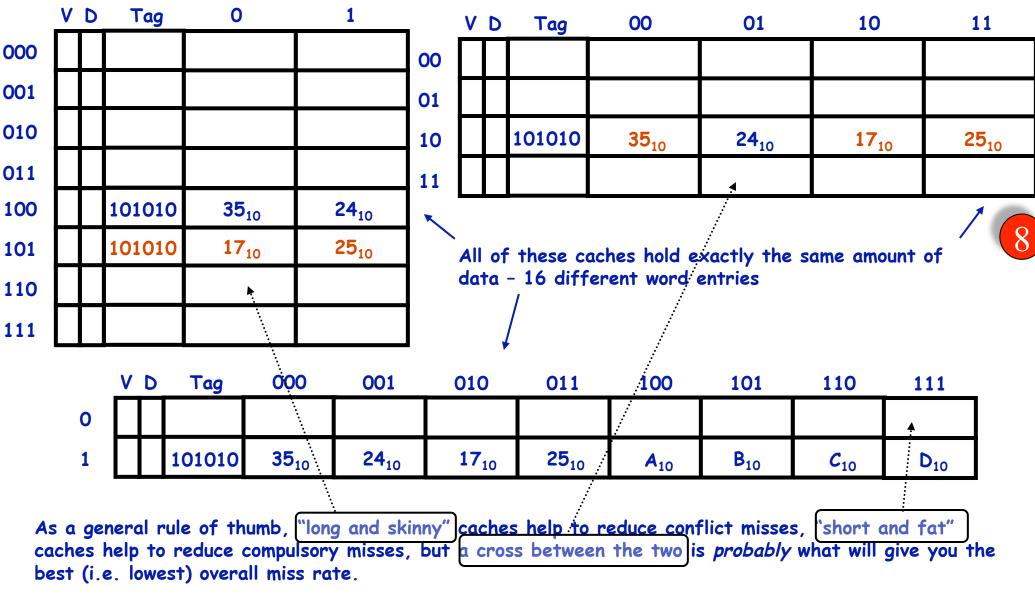

Thus, to avoid <u>capacity</u> <u>misses</u>, we'd need to make our cache <u>physically bigger</u> – i.e. there are now 32 word entries for it instead of 16.

FYI, this will change the way the physical address is divided. Given our original pattern of accesses, we'd have:

#### Pattern of accesses:

| 1.) | 10101 | 010 | $00 = 35_{10}$ |

|-----|-------|-----|----------------|

| 2.) | 10101 | 010 | $01 = 24_{10}$ |

| 3.) | 10101 | 010 | $10 = 17_{10}$ |

| 4.) | 10101 | 010 | $11 = 25_{10}$ |

(note smaller tag, bigger index)