### CMOS VLSI Design

### **CMOS Processing**

Peter Kogge University of Notre Dame Fall 2015, 2018

Based on material from

Prof. Jay Brockman, Joseph Nahas, University of Notre Dam

Prof. David Harris, Harvey Mudd College

http://www.cmosvlsi.com/coursematerials.html

### **Outline**

- □ CMOS Physical Structure

- ☐ Photolithography (Using light to define objects)

- ❖ Positive

- ❖ Negative

- □ Fabrication Overview

- ☐ Fabrication Step-by-Step

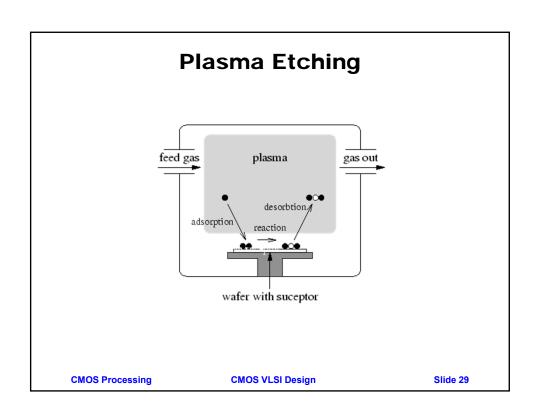

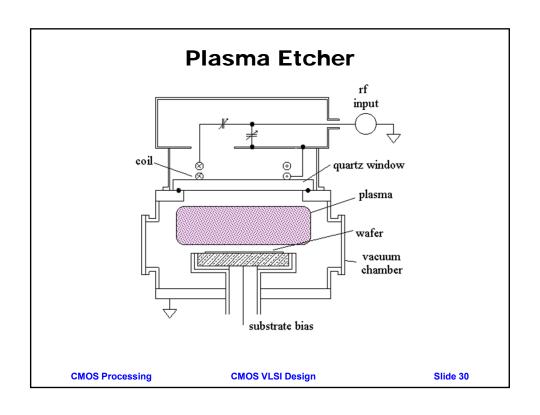

- Etching (Removal of material)

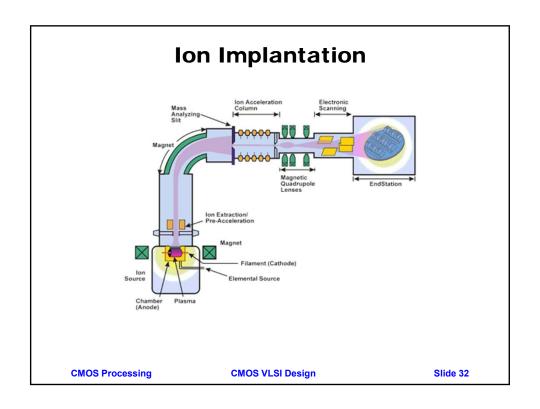

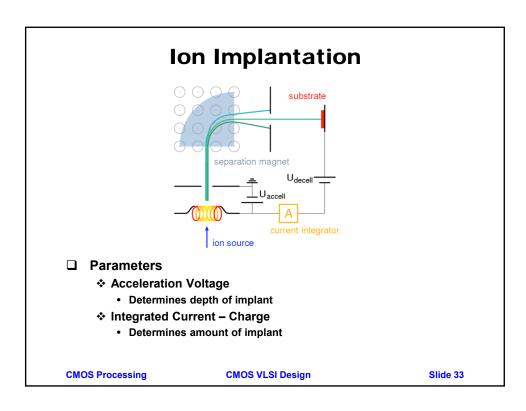

- Doping of Semiconductor (Adding donor and acceptors)

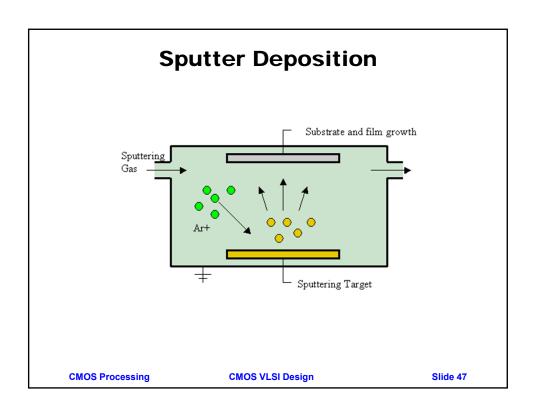

- Deposition (Adding material on top of wafer)

- **□** Newer Processes

**CMOS Processing**

**CMOS VLSI Design**

Slide 2

### **CMOS Cross Sections**

**CMOS Processing**

**CMOS VLSI Design**

Slide 3

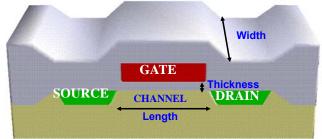

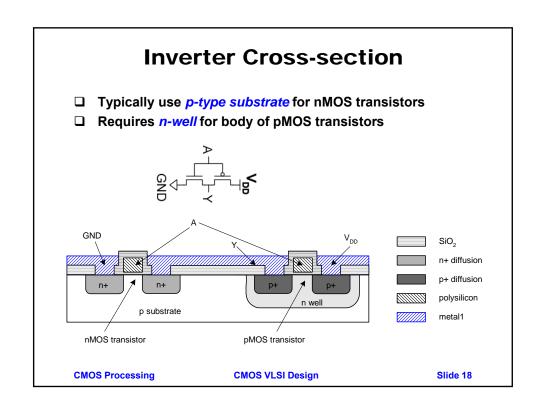

### **MOS Transistor Cross-section**

- □ Key Controlling Physical Parameters

- ❖ Length (L) of channel

- ❖ Width (W) of Channel

- ❖ Thickness (t<sub>ox</sub>)of gate insulator

- Material types

- ❖ N-type: Phosphorous doped to provide "free" electrons

- ❖ P-type: Boron doped to provide "free" positive holes

Circuits-A CMOS VLSI Design Slide 4

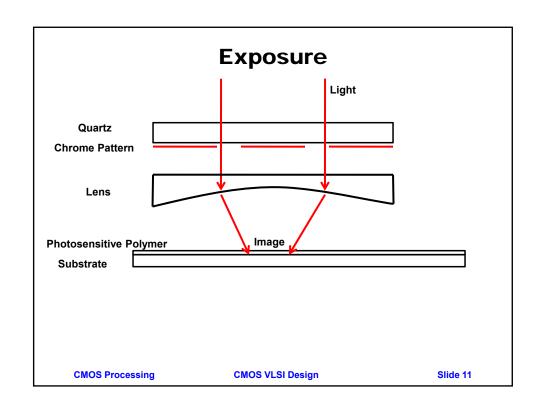

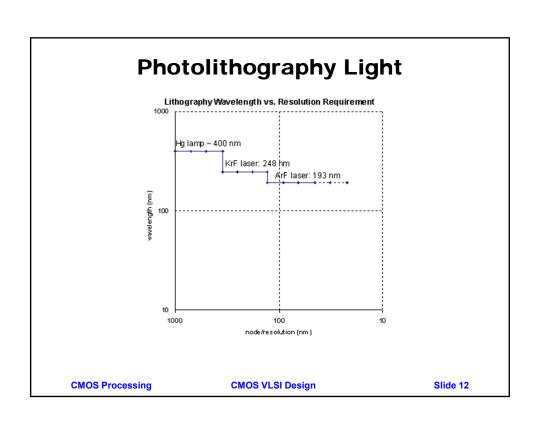

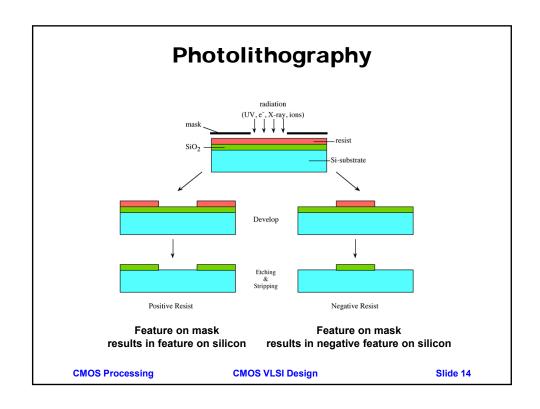

### Photolithography Aka "optical lithography" Selectively remove parts of a thin film on top of a substrate or the bulk of a substrate. Uses light to transfer geometric pattern from photo mask to light-sensitive chemical photo resist, ("resist"), on the substrate. Series of chemical treatments engraves exposure pattern into material underneath the photo resist.

### **Photolithography**

- □ Process of transferring geometric shapes on a mask (quartz glass plate) to the surface of a silicon wafer.

- Mask is created using a photolithographic process with an electron beam to scan the images on the plate.

**CMOS Processing**

**CMOS VLSI Design**

Slide 13

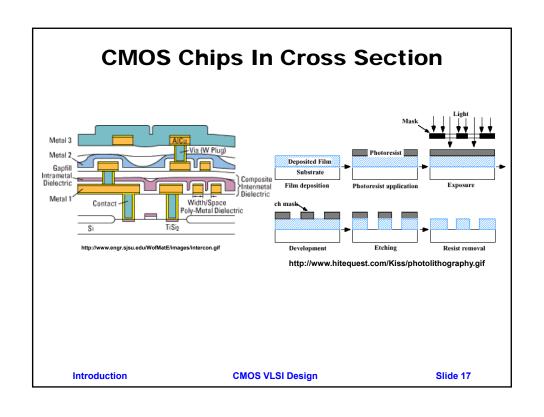

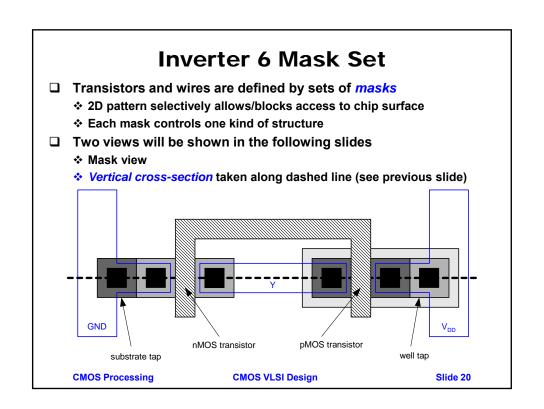

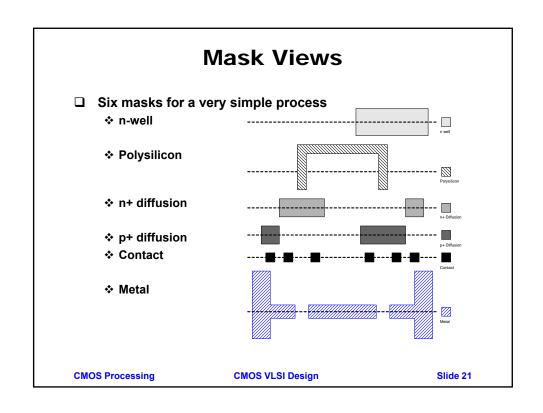

### CMOS Fabrication CMOS transistors fabricated on silicon wafer ❖ One wafer contains tens to thousands of chips ❖ Today wafers are up to 300 mm across Photolithography process "prints" patterns on the wafer. On each step, different materials are deposited or etched Easiest to understand: view both top and cross-section of wafer in a simplified manufacturing process, circa 1980.

### Fabrication Step by Step CMOS Processing CMOS VLSI Design Slide 22

### Fabrication Steps | Start with blank wafer | Build inverter from the bottom up | First step will be to form the n-well | Cover wafer with protective layer of SiO<sub>2</sub> (oxide) | Remove layer where n-well should be built | Implant or diffuse n dopants into exposed wafer | Strip off SiO<sub>2</sub> | Psubstrate | CMOS Processing | CMOS VLSI Design | Slide 24

## n-well: Oxidation Grow SiO<sub>2</sub> on top of Si wafer 900 – 1200 C with H<sub>2</sub>O or O<sub>2</sub> in oxidation furnace SiO<sub>2</sub> p substrate CMOS Processing CMOS VLSI Design Slide 25

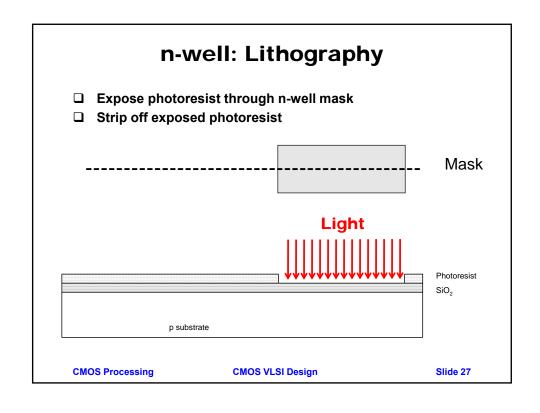

| n-well: Photoresist                                                                                                                                                                     |                  |                              |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------|--|--|

| <ul> <li>□ Spin on <i>photoresist</i></li> <li>❖ Photoresist is a light-sensitive organic polymer</li> <li>❖ Softens (positive) or hardens (negative) where exposed to light</li> </ul> |                  |                              |  |  |

|                                                                                                                                                                                         |                  | Photoresist SiO <sub>2</sub> |  |  |

| p subs                                                                                                                                                                                  | trate            |                              |  |  |

| CMOS Processing                                                                                                                                                                         | CMOS VLSI Design | Slide 26                     |  |  |

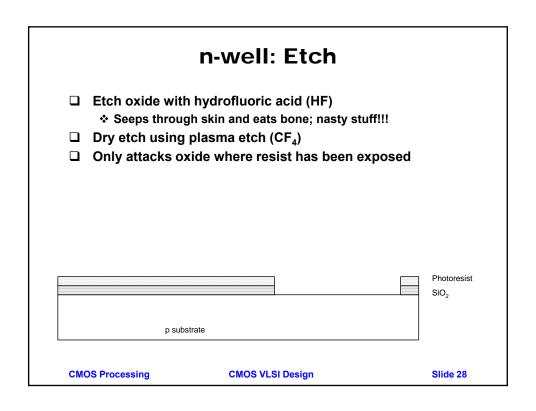

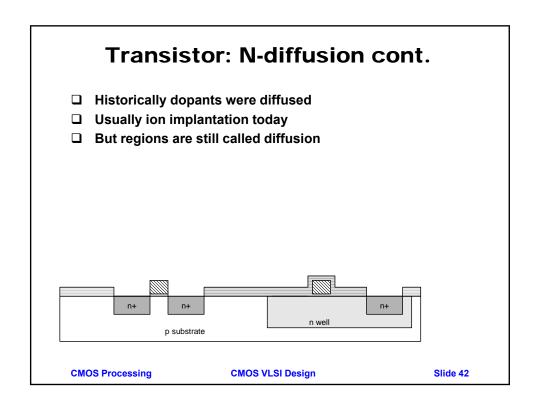

## n-well: Diffusion n-well is formed with diffusion or ion implantation Diffusion Place wafer in furnace with arsenic (As) gas Heat until As atoms diffuse into exposed Si Ion Implanatation Blast wafer with beam of As ions Ions blocked by SiO<sub>2</sub>, only enter exposed Si

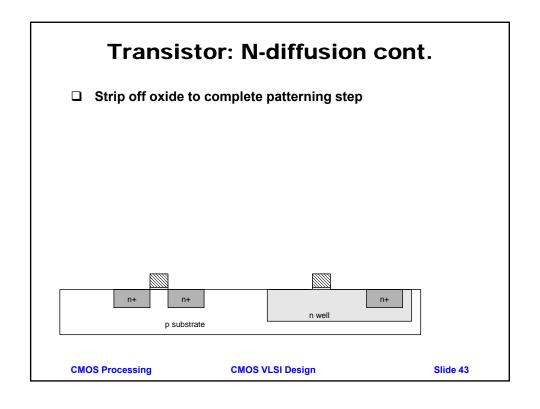

| n-well: Strip Oxide                                                                                                                                                |                  |          |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|--|

| <ul> <li>□ Strip off the remaining oxide using HF</li> <li>□ Back to bare wafer with n-well</li> <li>□ Subsequent steps involve similar series of steps</li> </ul> |                  |          |  |

|                                                                                                                                                                    |                  |          |  |

|                                                                                                                                                                    |                  |          |  |

| p sub                                                                                                                                                              | n well           |          |  |

| CMOS Processing                                                                                                                                                    | CMOS VLSI Design | Slide 34 |  |

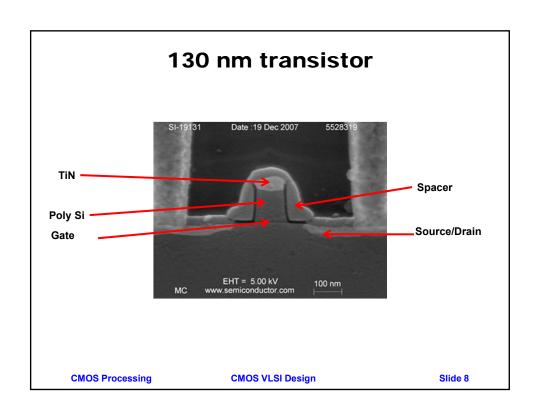

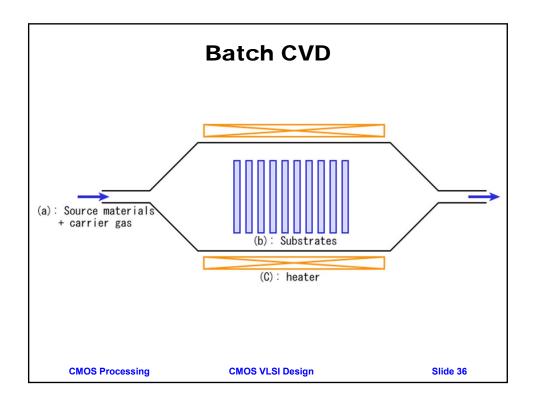

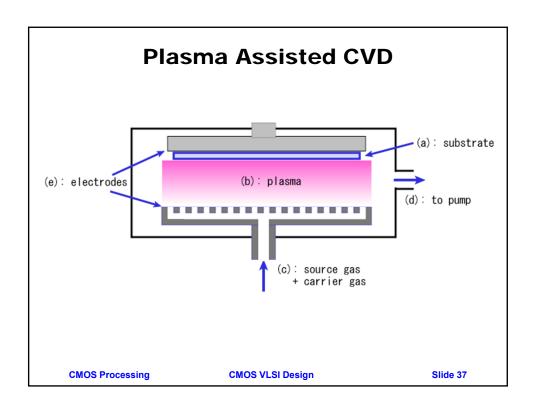

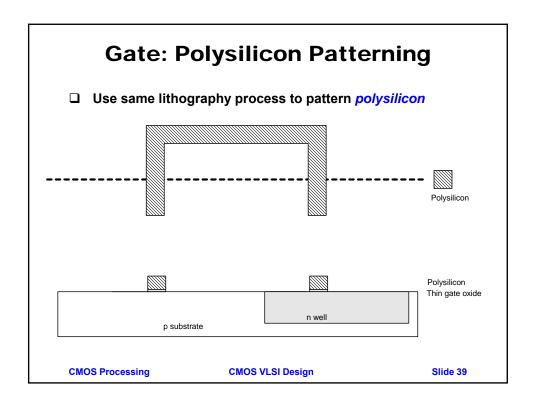

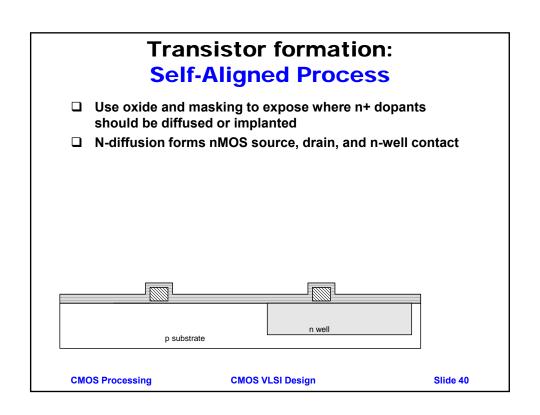

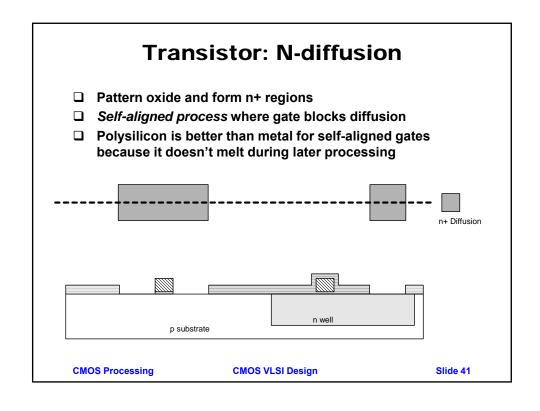

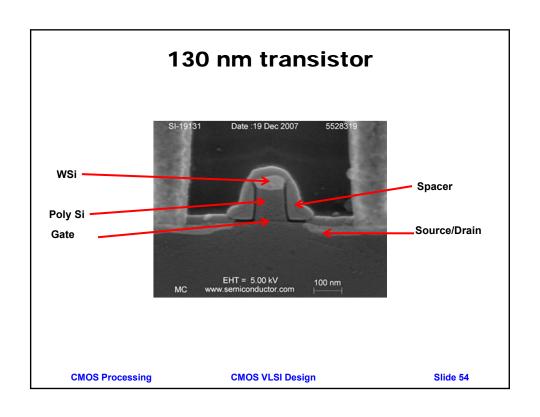

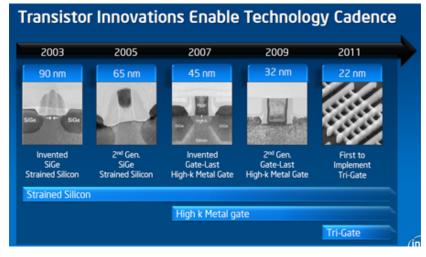

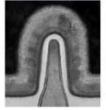

### **Forming the Gates** ☐ Deposit very thin layer of gate oxide ❖ < 20 Å (6-7 atomic layers) </p> ☐ Chemical Vapor Deposition (CVD) of silicon layer ❖ Place wafer in furnace with Silane gas (SiH₄) ❖ Forms many small crystals called polysilicon Heavily doped to be good conductor ☐ When the acronym "MOS" was invented, Al was used for the gate, instead of polysilicon. ☐ In 45 nm technology, metal gates and hafnium oxide are used. Thin gate oxide p substrate **CMOS VLSI Design** Slide 35 CMOS Processing

### CVD Reactions Silicon SiH<sub>4</sub> $\rightarrow$ Si + 2 H<sub>2</sub> Silicon Dioxide SiH<sub>4</sub> + O<sub>2</sub> $\rightarrow$ SiO<sub>2</sub> + 2 H<sub>2</sub> Silicon Nitride Silicon Nitride SiH<sub>4</sub> + 4 NH<sub>3</sub> $\rightarrow$ Si<sub>3</sub>N<sub>4</sub> + 12 H<sub>2</sub> Metal String Metal

**CMOS VLSI Design**

Slide 38

**CMOS Processing**

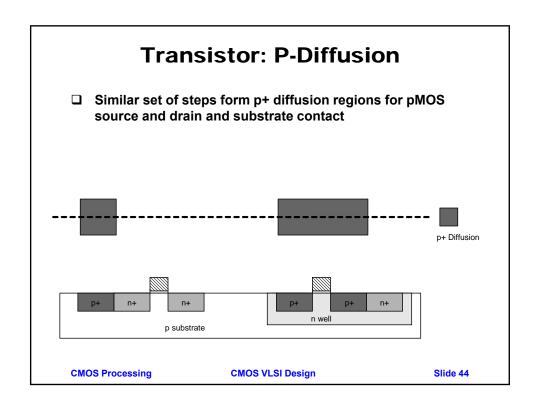

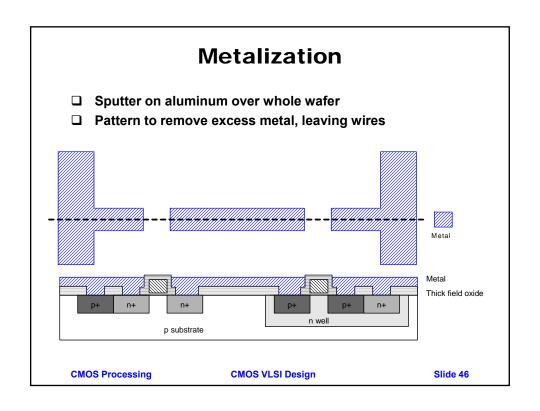

# Forming Contacts Now we need to wire together the devices Cover chip with thick field oxide Etch oxide where contact cuts are needed Contact Contact Thick field oxide CMOS Processing CMOS VLSI Design Slide 45

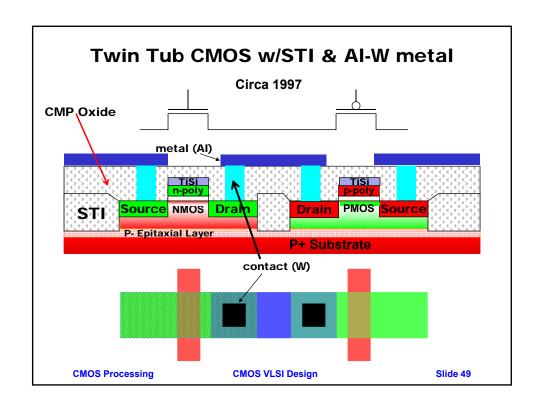

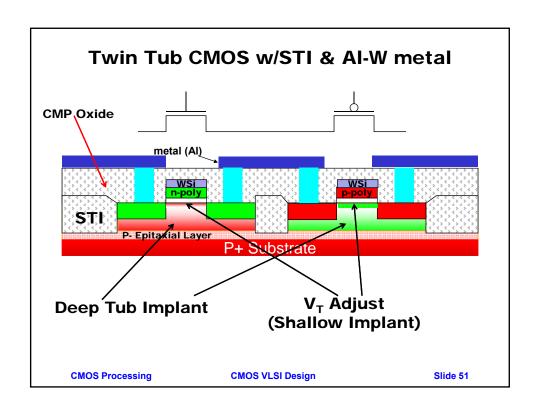

### Advanced Processes CMOS Processing CMOS VLSI Design Slide 48

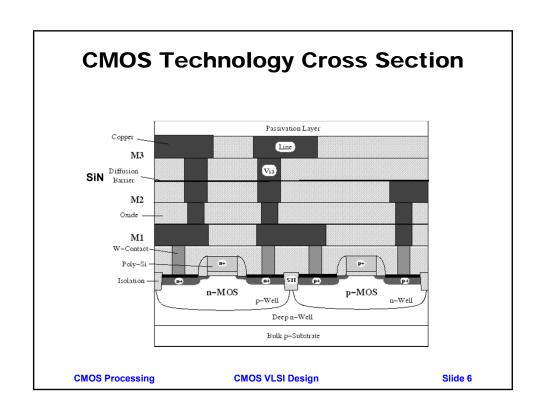

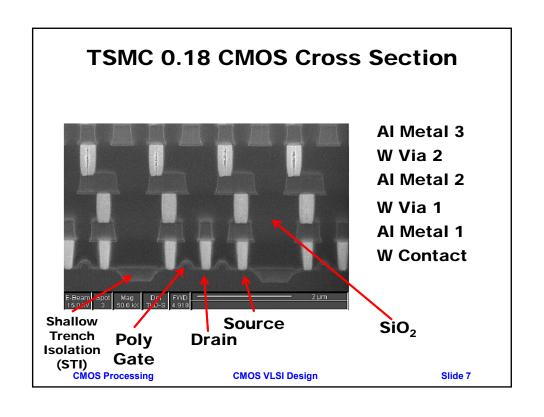

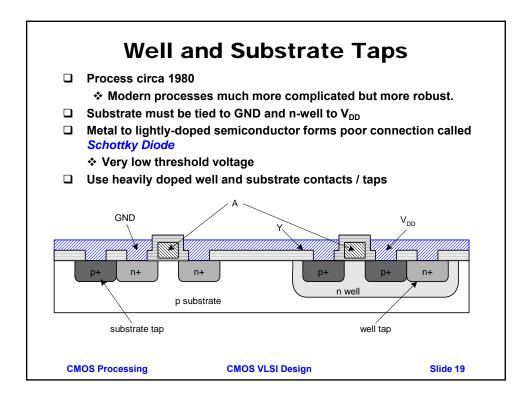

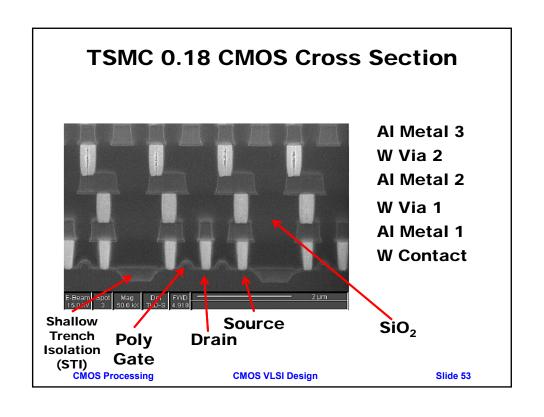

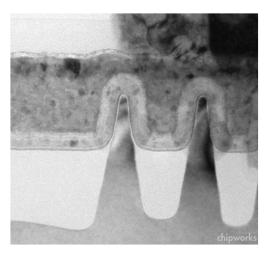

### Why Changes? ☐ CMP Oxide ❖ Chemical Mechanical Polishing (CMP) ❖ Flatten surface to enable multiple levels of metal ☐ Tungsten (W) contacts and Vias ❖ Enable use of CMP □ P+ Substrate \* Reduce substrate resistance and thus reduce latch-up. ☐ P- Epi ❖ Needed to enable p and n transistor tub doping with P+ **Substrate** □ Shallow Trench Isolation (STI) \* Reduce source and drain capacitance \* Reduce source and drain spacing □ Tungsten-Silicide \* Reduce gate resistance **CMOS Processing CMOS VLSI Design** Slide 50

http://www.zdnet.com/blog/computers/why-intels-22nm-technology-really-matters/5703

**CMOS Processing**

**CMOS VLSI Design**

Slide 55

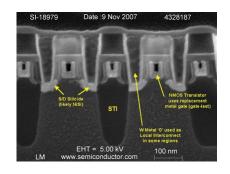

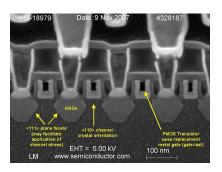

### **Intel 45 nm Transistor**

http://www.eetimes.com/design/automotive-design/4004782/Under-the-Hood-Intel-s-45-nm-high-k-metal-gate-process

**CMOS Processing**

**CMOS VLSI Design**

lide 56

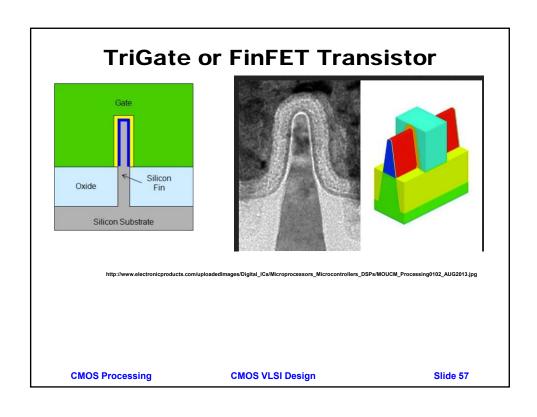

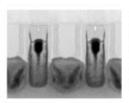

### Intel 22 nm Tri-gate Transistor

$http://www.electroiq.com/blogs/chipworks\_real\_chips\_blog/2012/04/intel-s-22-nm-trigate-transistors-exposed.html$

**CMOS Processing**

**CMOS VLSI Design**

Slide 59

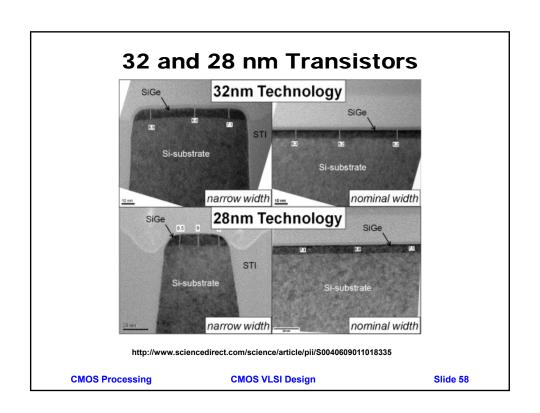

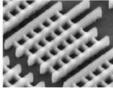

### 10nm FINFET

Logic

-High Speed

(HP/SP)

- Low Power

(LP/ULP)

High Voltage

$http://www.electronic products.com/uploaded Images/Digital\_ICs/Microprocessors\_Microcontrollers\_DSPs/MOUCM\_Processing 0103\_AUG 2013.jpg$

**CMOS Processing**

**CMOS VLSI Design**

Slide 60