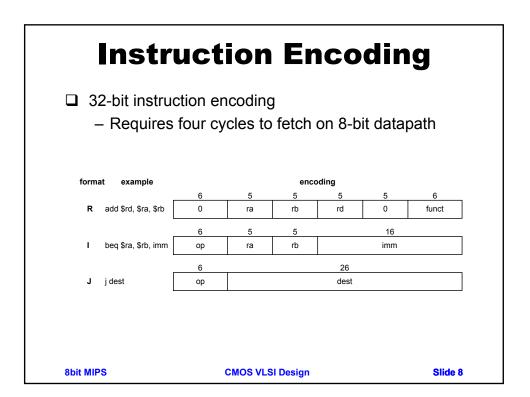

| Table 1.7 MIPS i  | nstruction set ( | subset supported)                         |          |        |       |

|-------------------|------------------|-------------------------------------------|----------|--------|-------|

| Instruction       | Function         |                                           | Encoding | ор     | funct |

| add \$1, \$2, \$3 | addition:        | \$1 → \$2 + \$3                           | R        | 000000 | 10000 |

| sub \$1, \$2, \$3 | subtraction:     | \$1 → \$2 - \$3                           | R        | 000000 | 10001 |

| and \$1, \$2, \$3 | bitwise and:     | \$1 → \$2 and \$3                         | R        | 000000 | 10010 |

| or \$1, \$2, \$3  | bitwise or:      | \$1 → \$2 or \$3                          | R        | 000000 | 10010 |

| slt \$1, \$2, \$3 | set less than:   | \$1 → 1 if \$2 < \$3<br>\$1 → 0 otherwise | R        | 000000 | 10101 |

| addi \$1, \$2,    | add immediate:   | \$1→ \$2 + imm                            | I        | 001000 | n/a   |

| beq \$1, \$2, imm | branch if equal: | $PC \rightarrow PC + imm^a$               | I        | 000100 | n/a   |

| j destination     | jump:            | PC destination <sup>a</sup>               | J        | 000010 | n/a   |

| lb \$1, imm(\$2)  | load byte:       | \$1 → mem[\$2 + imm]                      | I        | 100000 | n/a   |

| sb \$1, imm(\$2)  | store byte:      | mem[\$2 + imm] → \$1                      | I        | 110000 | n/a   |

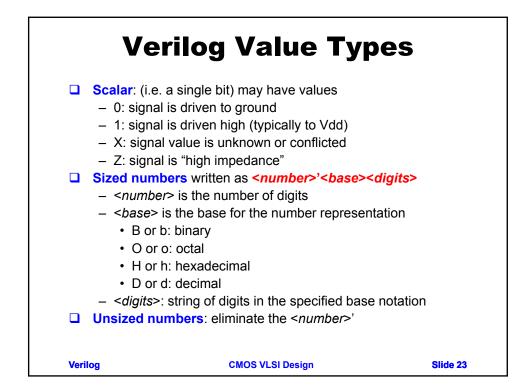

| Table A.2    | Constants |             |                    |              |

|--------------|-----------|-------------|--------------------|--------------|

| Number       | # Bits    | Base        | Decimal Equivalent | Stored       |

| 3'b101       | 3         | Binary      | 5                  | 101          |

| 'b11         | unsized   | Binary      | 3                  | 00000000011  |

| 8′b11        | 8         | Binary      | 3                  | 00000011     |

| 8'b1010_1011 | 8         | Binary      | 171                | 10101011     |

| 3′d6         | 3         | Decimal     | 6                  | 110          |

| 6′042        | 6         | Octal       | 34                 | 100010       |

| 8'hAB        | 8         | Hexadecimal | 171                | 10101011     |

| 42           | unsized   | Decimal     | 42                 | 000000101010 |

| Table A.1   | <b>Operator Precedence</b>  |            |

|-------------|-----------------------------|------------|

| Symbol      | Meaning                     | Precedence |

| ~           | NOT                         | Highest    |

| *, /, %     | MUL, DIV, MODULO            |            |

| +, -        | PLUS, MINUS                 |            |

| <<,>>,      | Logical Left/Right Shift    |            |

| <<<, >>>    | Arithmetic Left/Right Shift |            |

| <, <=, >, > | = Relative Comparison       |            |

| ==, !=      | Equality Comparison         |            |

| &, ~&       | AND, NAND                   |            |

| ^, ~^       | XOR, XNOR                   |            |

| , ~         | OR, NOR                     |            |

| ?:          | Conditional                 | Lowest     |

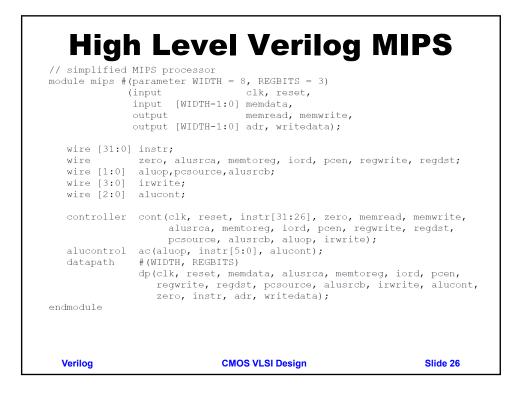

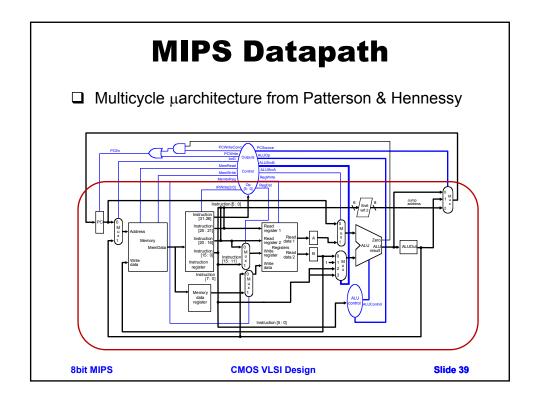

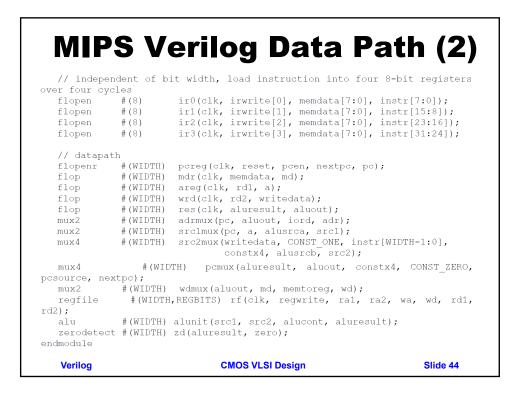

| MIPS Ve                                                                                 | erilog DataF                                                                                                      | Path (1)         |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------|

| input                                                                                   |                                                                                                                   | eg, iord, pcen,  |

| input [<br>input [<br>output<br>output [                                                | 1:0] pcsource, alusrcb,<br>3:0] irwrite,<br>2:0] alucont,<br>zero,<br>31:0] instr,<br>WIDTH-1:0] adr, writedata); |                  |

| // size of the paramete<br>parameter CONST_ZERO =<br>parameter CONST_ONE =              |                                                                                                                   | DTH parameter    |

|                                                                                         | ra2, wa;<br>xtpc, md, rd1, rd2, wd, a, src1,<br>aluout, constx4;                                                  | src2, aluresult, |

| // shift left constant<br>assign constx4 = {instr                                       |                                                                                                                   |                  |

| <pre>// register file addres assign ra1 = instr[REGB assign ra2 = instr[REGB mux2</pre> | ITS+20:21];                                                                                                       | [REGBITS+10:11], |

| Verilog                                                                                 | CMOS VLSI Design                                                                                                  | Slide 43         |

| module alu #(paran<br>(inpu<br>inpu | havioral AL<br>meter WIDTH = 8)<br>t [WIDTH-1:0] a, b,<br>t [2:0] alucont<br>ut reg [WIDTH-1:0] result) | ,               |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------|

| wire [WIDT]                         | H-1:0] b2, sum, slt;                                                                                    |                 |

| assign sum = a                      | ucont[2] ? ~b:b;<br>+ b2 + alucont[2];<br>be 1 if most significant b<br>um[WIDTH-1];                    | oit of sum is 1 |

| always@(*)                          |                                                                                                         |                 |

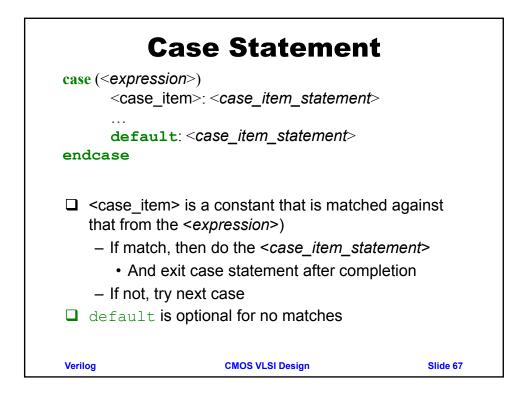

| case (alucon                        | esult <= a & b;                                                                                         |                 |

|                                     | esult <= a   b;                                                                                         |                 |

|                                     | esult <= sum;                                                                                           |                 |

| 2'b11: r                            | esult <= slt;                                                                                           |                 |

| endcase                             |                                                                                                         |                 |

| endmodule                           |                                                                                                         |                 |

| Verilog                             | CMOS VLSI Design                                                                                        | Slide 46        |