## **SCMOS Layout Rules - Via**

Vias must be drawn orthogonal to the grid of the layout. Non-Manhattan vias are not allowed.

| Rule | Description                                                                                                                                                           | Lambda          |      |      |                  |       |       |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|------|------------------|-------|-------|--|

|      |                                                                                                                                                                       | 2 Metal Process |      |      | 3+ Metal Process |       |       |  |

|      |                                                                                                                                                                       | SCMOS           | SUBM | DEEP | SCMOS            | SUBM  | DEEP  |  |

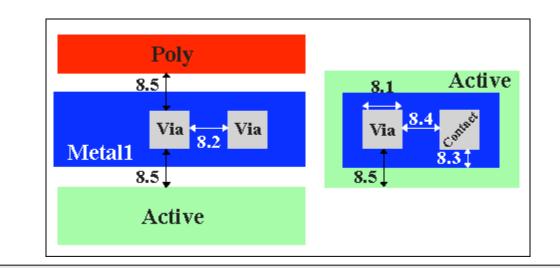

| 8.1  | Exact size                                                                                                                                                            | 2 x 2           | n/a  | n/a  | 2 x 2            | 2 x 2 | 3 x 3 |  |

| 8.2  | Minimum via1 spacing                                                                                                                                                  | 3               | n/a  | n/a  | 3                | 3     | 3     |  |

| 8.3  | Minimum overlap by metal1                                                                                                                                             | 1               | n/a  | n/a  | 1                | 1     | 1     |  |

| 8.4  | Minimum spacing to contact for<br>technology codes mapped to<br>processes that do not allow<br><u>stacked vias</u> (SCNA, SCNE,<br>SCN3M, SCN3MLC)                    | 2               | n/a  | n/a  | 2                | 2     | n/a   |  |

| 8.5  | Minimum spacing to poly or active<br>edge for technology codes<br>mapped to processes that do not<br>allow <u>stacked vias</u> (NOTE: list is<br>not same as for 8.4) | 2               | n/a  | n/a  | 2                | 2     | n/a   |  |

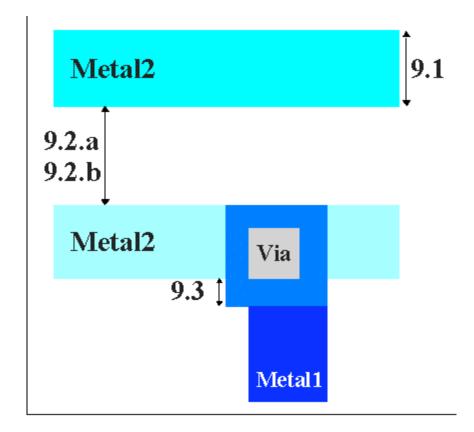

## SCMOS Layout Rules - Metal2

| Rule | Description                                                          | Lambda          |      |      |                  |      |      |  |

|------|----------------------------------------------------------------------|-----------------|------|------|------------------|------|------|--|

|      |                                                                      | 2 Metal Process |      |      | 3+ Metal Process |      |      |  |

|      |                                                                      | SCMOS           | SUBM | DEEP | SCMOS            | SUBM | DEEP |  |

| 9.1  | Minimum width                                                        | 3               | n/a  | n/a  | 3                | 3    | 3    |  |

| 9.2  | Minimum spacing                                                      | 3               | n/a  | n/a  | 3                | 3    | 4    |  |

| 9.3  | Minimum overlap of via1                                              | 1               | n/a  | n/a  | 1                | 1    | 1    |  |

| 9.4  | Minimum spacing when either<br>metal line is wider than 10<br>lambda | 6               | n/a  | n/a  | 6                | 6    | 8    |  |