| OPCODE | Mnemonic | RTL (What does the instruction do) |

|--------|----------|------------------------------------|

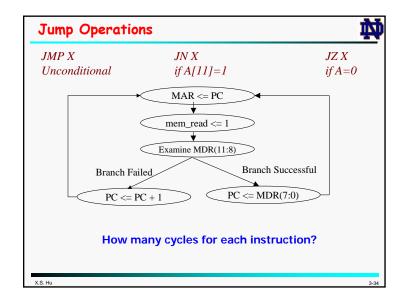

| 0000   | JMP X    | PC <- X                            |

| 0001   | JN X     | if A<0 then PC <-X else PC++       |

| 0010   | JZ X     | if A=0 then PC <-X else PC++       |

| 0011   | reserved |                                    |

| 0100   | LOAD X   | A <- M(X), PC++                    |

| 0101   | STORE X  | M(X) <- A, PC++                    |

| 0110   | reserved |                                    |

| 0111   | reserved |                                    |

| 1000   | AND X    | A <- A and $M(X)$ , PC++           |

| 1001   | OR X     | A <- A or M(X), PC++               |

| 1010   | ADD X    | A <- A + M(X), PC++                |

| 1011   | SUB X    | A <- A - M(X), PC++                |

| 1100   | reserved |                                    |

| 1101   | reserved |                                    |

| 1110   | reserved |                                    |

| 1111   | reserved |                                    |

| 0<br>1<br>2<br>3<br>4<br>5 B1:<br>6 SAVE: | LOAD X<br>SUB Y<br>JN B1<br>LOAD X<br>JMP SAVE<br>LOAD Y<br>STORE Z |  |

|-------------------------------------------|---------------------------------------------------------------------|--|

| Program E                                 | execution (1)                                                       |                          |                        | 政   |

|-------------------------------------------|---------------------------------------------------------------------|--------------------------|------------------------|-----|

| PROGRAM                                   |                                                                     | VAL                      | <u>UE IN A</u>         |     |

| 0<br>1<br>2<br>3<br>4<br>5 B1:<br>6 SAVE: | LOAD X<br>SUB Y<br>JN B1<br>LOAD X<br>JMP SAVE<br>LOAD Y<br>STORE Z | 10<br>5<br>5<br>10<br>10 | (not taken)<br>(taken) |     |

| Х:<br>Ү:<br>Z:                            | 10<br>5<br>n/a                                                      |                          |                        | 3-9 |

| PROGRAM                                   | 1              | VALUE IN A |  |

|-------------------------------------------|----------------|------------|--|

| 0<br>1<br>2<br>3<br>4<br>5 B1:<br>6 SAVE: | -              | 5          |  |

| X:<br>Y:<br>Z:                            | 10<br>5<br>n/a |            |  |

| PROGRAM | VALUE                                                                  | IN A |

|---------|------------------------------------------------------------------------|------|

| 2       | LOAD X<br>SUB Y<br>JN B1<br>LOAD X<br>JMP SAVE 10<br>LOAD Y<br>STORE Z |      |

| :       | 10<br>5<br>0/a                                                         |      |

| Program E×                                        | ecution (6)                                                         |            | ₩    |

|---------------------------------------------------|---------------------------------------------------------------------|------------|------|

| PROGRAM                                           |                                                                     | VALUE IN A |      |

| 0<br>1<br>2<br>3<br>4<br>5 B1:<br><b>6 SAVE</b> : | LOAD X<br>SUB Y<br>JN B1<br>LOAD X<br>JMP SAVE<br>LOAD Y<br>STORE Z | 10         |      |

| X:<br>Y:<br>Z:                                    | 10<br>5<br>10                                                       |            |      |

| X.S. Hu                                           |                                                                     |            | 3-13 |

| ; A program to see if each     | L1:      | LOAD  | AO   |  |

|--------------------------------|----------|-------|------|--|

| : item in array contains a     | <b>_</b> | JZ    | Done |  |

| ; particular element           |          | AND   | Mask |  |

| ; while (A[i] != 0)            |          | JZ    | B1   |  |

| ; if ( A[i] & Mask !=0)        |          | LOAD  | One  |  |

| ; A[i] = 1;                    |          | JMP   | L2   |  |

| ; else                         | B1:      | LOAD  | Zero |  |

| ; $A[i] = 0;$                  | L2:      | STORE | A0   |  |

| ; i++;<br>; Data declarations! |          |       |      |  |

| , DATA A0 3                    |          | LOAD  | L1   |  |

| .DATA A0 3                     |          | ADD   | One  |  |

| .DATA A2 3                     |          | STORE | L1   |  |

| .DATA A3 8                     |          | LOAD  | L2   |  |

| .DATA A4 19                    |          | ADD   | One  |  |

| .DATA A5 0                     |          | STORE | L2   |  |

| .DATA Zero 0                   | Danas    | JMP   | L1   |  |

| .DATA One 1                    | Done:    |       |      |  |

| .DATA Mask 1                   |          | .END  |      |  |

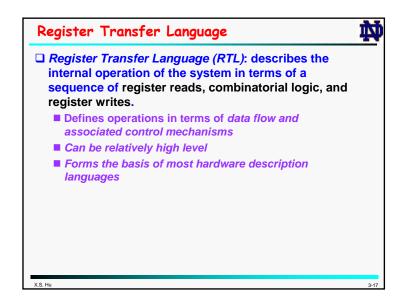

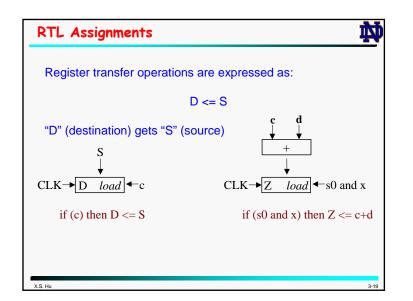

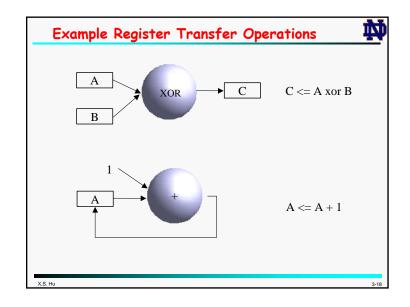

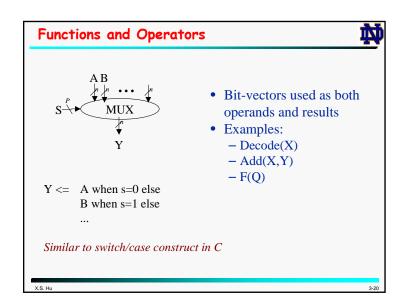

| Registers<br>Transfer into ("gets")<br>indicates a control state<br>parallel microoperations<br>Arithmetic Operations | A, B, foo<br>A <= B<br>s0: <statement><br/>A&lt;=B,C&lt;=D<br/>A&lt;=B+1</statement> |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Transfer into ("gets")<br>indicates a control state<br>parallel microoperations                                       | A <= B<br>s0: <statement><br/>A&lt;=B,C&lt;=D</statement>                            |

| indicates a control state parallel microoperations                                                                    | s0: <statement><br/>A&lt;=B,C&lt;=D</statement>                                      |

| parallel microoperations                                                                                              | A<=B,C<=D                                                                            |

|                                                                                                                       | ,                                                                                    |

| Arithmetic Operations                                                                                                 | $A \le B+1$                                                                          |

|                                                                                                                       |                                                                                      |

| logic operators (bitwise)                                                                                             | A<=A&B                                                                               |

| shift operators                                                                                                       | A<=B<<1                                                                              |

| conditional                                                                                                           | if (c=0) then                                                                        |

|                                                                                                                       | F<= 1                                                                                |

|                                                                                                                       | else F<= 0                                                                           |

| branch                                                                                                                | goto s0                                                                              |

|                                                                                                                       | 0                                                                                    |

|                                                                                                                       | More excercise                                                                       |

|                                                                                                                       | shift operators<br>conditional                                                       |

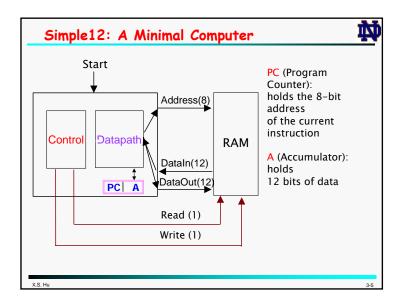

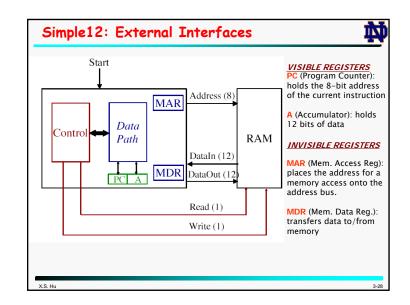

| Start<br>Address (8)<br>Control<br>Data<br>Dataln (12)<br>DataOut (12)<br>RAM<br>Read (1)<br>Write (1) | PC (Program Counter):<br>holds the 8-bit address<br>of the current instruction<br>A (Accumulator): holds<br>12 bits of data |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| OPCODE | Mnemonic | RTL                               |

|--------|----------|-----------------------------------|

| 0000   | JMP X    | PC <- X                           |

| 0001   | JN X     | if A<0 then PC <-X else PC++      |

| 0010   | JZ X     | if A=0 then PC <-X else PC++      |

| 0011   | reserved |                                   |

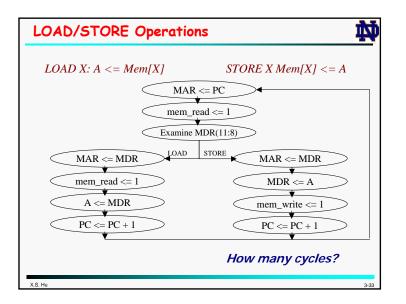

| 0100   | LOAD X   | A <- M(X), PC++                   |

| 0101   | STORE X  | M(X) <- A, PC++                   |

| 0110   | reserved |                                   |

| 0111   | reserved |                                   |

| 1000   | AND X    | $A \leq A$ and $M(X)$ , $PC++$    |

| 1001   | OR X     | $A \leq A \text{ or } M(X), PC++$ |

| 1010   | ADD X    | A <- A + M(X), PC++               |

| 1011   | SUB X    | A <- A - M(X), PC++               |

| 1100   | reserved |                                   |

| 1101   | reserved |                                   |

| 1110   | reserved |                                   |

| 1111   | reserved |                                   |

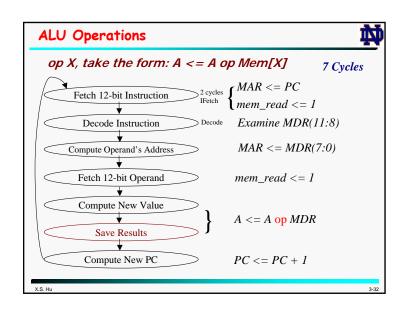

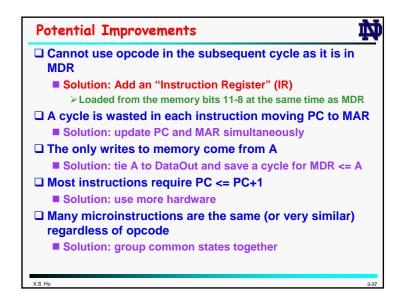

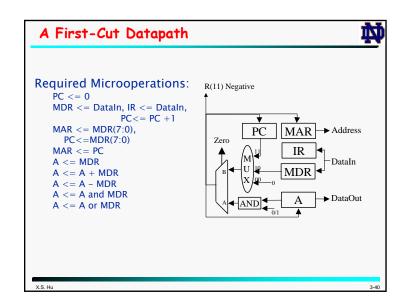

| Required Datapath Operations | 立    |

|------------------------------|------|

| ALU Instructions             |      |

| AND, OR, ADD, SUB            |      |

| PC Increment                 |      |

| LOAD/STORE Instructions      |      |

| Register Transfers Only      |      |

| PC Increment                 |      |

| JUMP Instructions            |      |

| Check A[11] and A=0          |      |

| ≻n_flag                      |      |

| ≻z_flag                      |      |

| Only Register Transfers      |      |

|                              |      |

|                              |      |

|                              |      |

| X.S. Hu                      | 3-35 |

|                    |                            | CYCL | E* PC   | Α    | MAR | MDR  | MEM OP    |

|--------------------|----------------------------|------|---------|------|-----|------|-----------|

| EXAMPLE            | E: Choose the max of two   | 1    | 00h     | -    | 0   | -    | -         |

|                    | numbers.                   | 2    | 00h     | -    | 0   | 430h | Read M[0] |

|                    |                            | 3    | 00h     | -    | 0   | 430h | -         |

| 00h:               | LOAD X (30h)               | 4    | 00h     | -    | 30h | 430h | -         |

| 01h:<br>02h:       | SUB Y (31h)<br>JN B1 (06h) | 5    | 00h     |      | 30h | 007h | Read M[30 |

| 0211:<br>03h:      | LOAD X (30h)               | 6    | 00h     | 007h | 30h | 007h |           |

| 04h:               | JMP SAVE (07h)             | 7    | 01h     | 007h | 30h | 007h | -         |

| 06h: B1:           | LOAD Y (31h)               | 8    | 01h     | 007h | 01h | 007h | -         |

| 07h: SAVE          | : STORE Z (32h)            | 9    | 01h     | 007h | 01h | B31h | Read M[01 |

|                    |                            | 10   | 01h     | 007h | 01h | B31h |           |

| •                  |                            | 11   | 01h     | 007h | 31h | B31h | -         |

| 201 W              | -                          | 12   | 01h     | 007h | 31h | 00Ah | Read M[31 |

| 30h: X:<br>31h: Y: | 7<br>10                    | 13   | 01h     | FFDh | 31h | 00Ah |           |

| 31n; Y;<br>32h; Z; | 10<br>n/a                  | 14   | 02h     | FFDh | 31h | 00Ah | -         |

| <u>5211. E.</u>    | n/a                        |      | of each |      |     |      |           |

| Stopped -Start <u>INSTRUCTION CYCLES</u><br>Start JMP 2<br>IFetch JN 2<br>JZ 2<br>LOAD 4 | Revised State Machine                                              |                                                      | 拉                               |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|---------------------------------|

| EAGenStoreSTORE3AND4OpAccessOR4ADD4ExecuteSUB4                                           | Stopped<br>VStart<br>IFetch<br>EAGen<br>Jumps<br>Store<br>OpAccess | JMP<br>JN<br>JZ<br>LOAD<br>STORE<br>AND<br>OR<br>ADD | 2<br>2<br>4<br>3<br>4<br>4<br>4 |

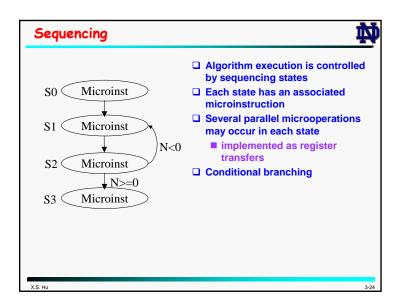

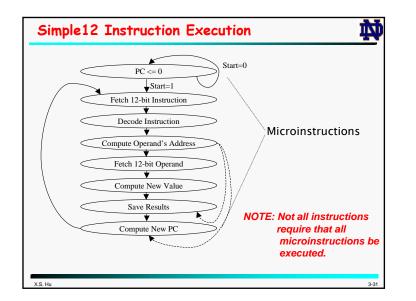

| Stopped      | If start=1 then (MAR <= 0, PC<=0, goto IFetch)          |

|--------------|---------------------------------------------------------|

|              | else goto Stopped                                       |

| IFetch:      | read_mem <= 1, MDR <= DataIn, MAR<=PC+1,                |

|              | PC<=PC+1, IR<=DataIn(11:8), goto EAGen                  |

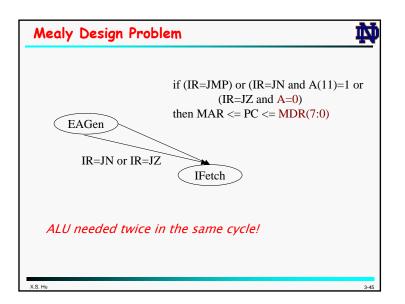

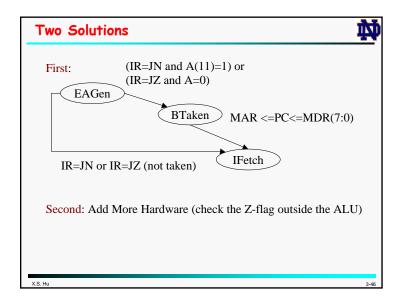

| EAGen:       | if (IR=JMP) or (IR=JN and A(11)=1) or (IR=JZ and A=0)   |

|              | then MAR <= MDR(7:0), PC<=MDR(7:0) goto IFetch          |

|              | else if (IR=JN) or (IR=JZ) then goto IFetch             |

|              | else MAR <= MDR(7:0), goto OpAccess                     |

| OpAccess:    | MAR <= PC,                                              |

|              | if IR=LOAD or IR(3:2)=10 /* i.e., an ALU operation */   |

|              | then (Read <= 1, MDR<=DataIn, goto Execute)             |

|              | else (Write <= 1, DataOut <= A, goto IFetch) /* a STORE |

| Execute:     | if (IR=LOAD) then A <= MDR, goto IFetch                 |

|              | else if (IR=AND) then A <= A and MDR, goto IFetch       |

|              | else if (IR=OR) then A <= A or MDR, goto IFetch         |

|              | else if (IR=ADD) then A <= A + MDR, goto IFetch         |

|              | else if (IR=SUB) then A <= A - MDR, goto IFetch         |

| NOTE: if Rea | d and Write are not explicitly specified, they are 0    |

| NOTE. II Kea | a and write are not explicitly specified, they are o    |

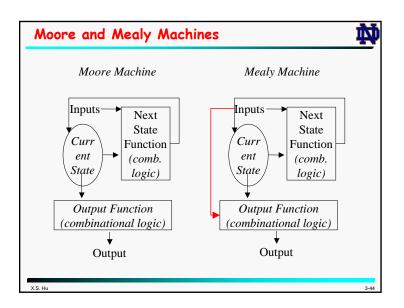

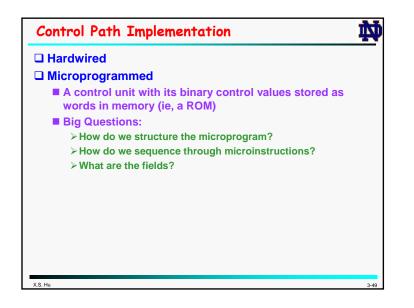

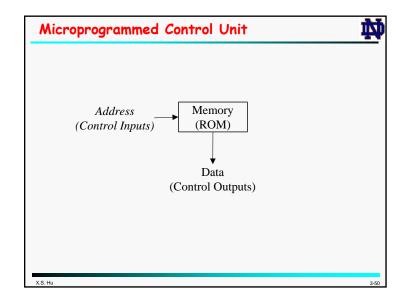

| Microinstruction state machine            | ons will be issued to the data path using a                                          |

|-------------------------------------------|--------------------------------------------------------------------------------------|

| Two possibiliti                           | es:                                                                                  |

| Moore Machies<br>only on the construction | ine: the outputs of the state machine depend surrent state                           |

| · · · · · · · · · · · · · · · · · · ·     | ne: the outputs of the state machine depend<br>nt state and the values of the inputs |

|                                           |                                                                                      |

|                                           |                                                                                      |

|                                           |                                                                                      |

|                                           |                                                                                      |

|                                           |                                                                                      |

|                                           |                                                                                      |

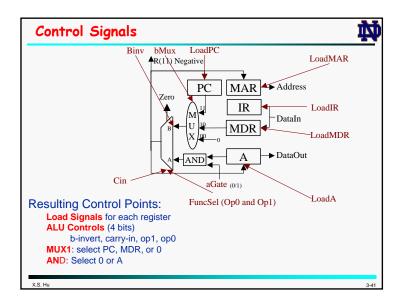

| <u>Binv</u> | Cin    | op1     | opO                 | ACTION    |

|-------------|--------|---------|---------------------|-----------|

| 0           | 0      | 0       | 0                   | A and B   |

| 1           | 0      | 0       | 0                   | A and ~B  |

| 0           | 0      | 0       | 1                   | A or B    |

| 1           | 0      | 0       | 1                   | A or ~B   |

| 0           | 0      | 1       | 0                   | A + B     |

| 0           | 1      | 1       | 0                   | A + B + 1 |

| 1           | 1      | 1       | 0                   | A - B     |

| 1           | 0      | 1       | 0                   | A - B + 1 |

| ALU         | also i | has a ' | "zero" fla <u>c</u> | 7.        |

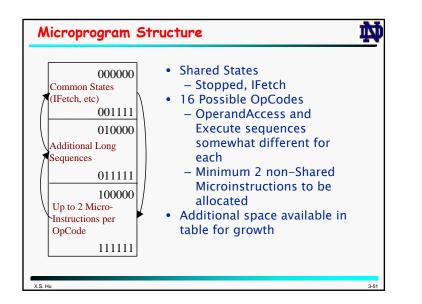

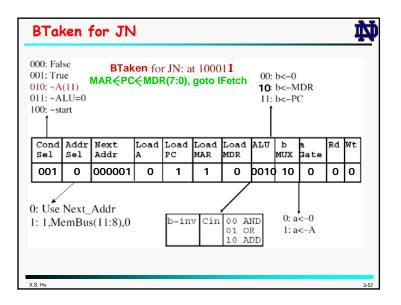

| <b>INSTRUCTION</b> | CYCLES |

|--------------------|--------|

| JMP                | 2      |

| JN not taken       | 2      |

| taken              | 3      |

| JZ not taken       | 2      |

| taken              | 3      |

| LOAD               | 4      |

| STORE              | 3      |

| AND                | 4      |

| OR                 | 4      |

| ADD                | 4      |

| SUB                | 4      |

| Q                                                                                                                                                                  | IR                                                                                                  | S<br>t<br>r<br>t | Neg           | Zero          | Q*                                                                                                                                                        | L<br>A                                                                                      | L<br>P<br>C                                                                                      | L<br>M<br>A<br>R                                                                                                     | L<br>M<br>D<br>R                                                                                 | L<br>I<br>R                                                             | A<br>L<br>U                                                  | b<br>M<br>U<br>X | a<br>Gate                                                                                        | R<br>e<br>a<br>d                                                   | W<br>r<br>i<br>t<br>e                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|---------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Stopped<br>Stopped<br>LFetch<br>EAGen<br>EAGen<br>EAGen<br>EAGen<br>EAGen<br>Opnd<br>Opnd<br>Opnd<br>Execute<br>Execute<br>Execute<br>Execute<br>Execute<br>Braken | n/a<br>JMP<br>JZ<br>JZ<br>LD/ST<br>ALUOP<br>LOAD<br>ALU<br>STORE<br>LOAD<br>AND<br>OR<br>ADD<br>SUB | 01               | n/a<br>0<br>1 | n/a<br>0<br>1 | Stopped<br>IFetch<br>EAGen<br>IFetch<br>IFetch<br>BTaken<br>BTaken<br>Opnd<br>Opnd<br>Execute<br>IFetch<br>IFetch<br>IFetch<br>IFetch<br>IFetch<br>IFetch | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1 | 0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | n/a<br>+<br>+<br>+<br>+<br>+<br>AND<br>OR<br>ADD<br>SUB<br>+ | MDR              | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |

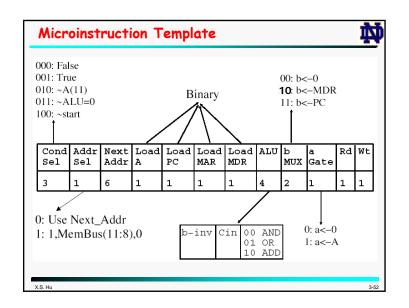

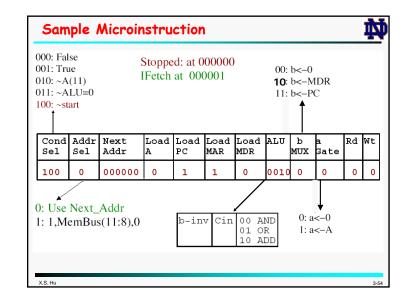

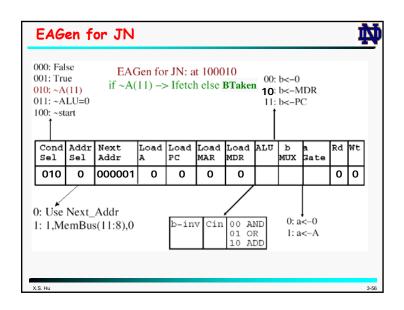

| 000: Fai<br>01: Tri<br>010: ~A<br>011: ~A<br>011: ~Si | ue<br>(11)<br>LU=0 |                   |           | 1: at 00<br>R<-P( |       | C+1         | 10   | b<-0<br>b<-M<br>b<-P |            |    |    |

|-------------------------------------------------------|--------------------|-------------------|-----------|-------------------|-------|-------------|------|----------------------|------------|----|----|

| Cond<br>Sel                                           | Addr<br>Sel        | Next<br>Addr      | Load<br>A |                   |       | Load<br>MDR |      | b<br>MUX             | a<br>Gate  | Rd | Wt |

| 001                                                   | 1                  |                   | 0         | 1                 | 1     | 1           | 0110 | 11                   | 0          | 1  | 0  |

|                                                       | Next_<br>emBus     | Addr<br>s(11:8),0 |           | b-in              | v Cin | 01 0        |      | 0: a<br>1: a         | <-0<br><-A |    |    |

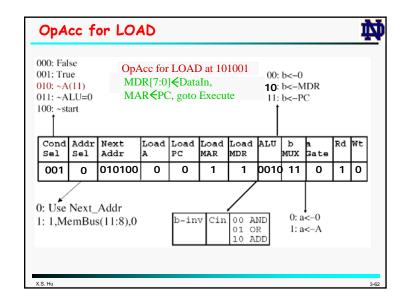

| 00: Fa<br>01: Tr<br>10: ~A<br>11: ~A<br>00: ~st | ue<br>(11)<br>LU=0 | OpA<br>MDR[7      |           | ADD<br>ataIn, g |             |             | 10            | b<-0<br>b<-N<br>b<-P |            |    |    |

|-------------------------------------------------|--------------------|-------------------|-----------|-----------------|-------------|-------------|---------------|----------------------|------------|----|----|

| Cond<br>Sel                                     | Addr<br>Sel        |                   | Load<br>A | Load<br>PC      | Load<br>MAR | Load<br>MDR |               | b<br>MUX             | a<br>Gate  | Rd | Wt |

| 001                                             | 0                  | 011010            | 0         | 0               | 0           | 1           |               |                      |            | 1  | 0  |

|                                                 | Next_<br>emBus     | Addr<br>s(11:8),0 |           | b-in            | v Cin       | 01 0        | ND<br>R<br>DD |                      | <-0<br><-A |    |    |

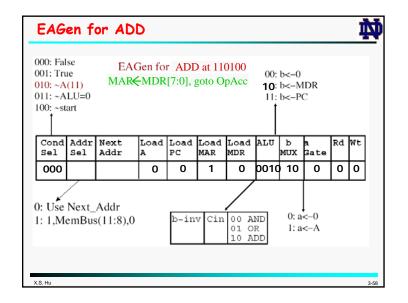

| EAG                                               | en f               | or LOA            | AD        |                   |       |             |               |                      |            |    | Į  |

|---------------------------------------------------|--------------------|-------------------|-----------|-------------------|-------|-------------|---------------|----------------------|------------|----|----|

| 00: Fal<br>01: Tru<br>10: ~A<br>11: ~A<br>00: ~st | ie<br>(11)<br>LU=0 | EAC<br>MAR€       |           | r LOA<br>[7:0], § |       |             | 10            | b<–0<br>b<–N<br>b<–P |            |    |    |

| Cond<br>Sel                                       | Addr<br>Sel        | Next<br>Addr      | Load<br>A | Load<br>PC        |       | Load<br>MDR |               | b<br>MUX             | a<br>Gate  | Rd | Wt |

| 000                                               |                    |                   | 0         | 0                 | 1     | 0           | 0010          | 10                   | 0          | 0  | 0  |

|                                                   | Next_<br>emBus     | Addr<br>s(11:8),0 |           | b-in              | v Cin | 01 0        | ND<br>R<br>DD |                      | <-0<br><-A |    |    |

| S Hu                                              |                    |                   |           |                   |       |             |               |                      |            |    |    |

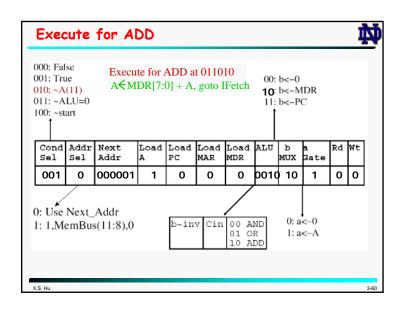

| 00: Fai<br>01: Tri<br>10: ~A<br>11: ~A<br>00: ~st | ie<br>(11)<br>LU=0 | Execu<br>A€M      |           | LOAD<br>0], goto |             |                        | 10   | b<-0<br>b<-M<br>b<-P0 |            |    |    |

|---------------------------------------------------|--------------------|-------------------|-----------|------------------|-------------|------------------------|------|-----------------------|------------|----|----|

| Cond<br>Sel                                       | Addr<br>Sel        | Next<br>Addr      | Load<br>A | Load<br>PC       | Load<br>MAR | Load<br>MDR            |      | b<br>MUX              | a<br>Gate  | Rd | Wt |

| 001                                               | 0                  | 000001            | 1         | 0                | 0           | 0                      | 0010 | 10                    | 0          | 0  | 0  |

|                                                   | Next_<br>emBus     | Addr<br>s(11:8),0 |           | b-in             | v Cin       | 00 Ai<br>01 0<br>10 Ai |      |                       | <-0<br><-A |    |    |