# MEMORY ARCHITECTURE FOR QUANTOM-DOT CELLULAR AUTOMATA

A Thesis

Submitted to the Graduate School of the University of Notre Dame in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Computer Science and Engineering

by

Sarah Elizabeth Frost, B.A.

Dr. Peter Kogge, Director

Graduate Program in Computer Science and Engineering Notre Dame, Indiana March 2005

# MEMORY ARCHITECTURE FOR QUANTOM-DOT CELLULAR AUTOMATA

Abstract

by

# Sarah Elizabeth Frost

Quantum-dot Cellular Automata (QCA) is a novel nanotechnology with great potential for very dense memory and low power logic. This work presents the Hmemory architecture, a memory architecture that exploits the characteristics of QCA and results in order of magnitude density gains over end of the roadmap SRAM and DRAM. Two enhancements to the basic architecture are also presented, including a complete merging of processor and memory. Finally, a novel clocking wire layout is presented and its effect on architecture discussed. This thesis is dedicated to my parents, Thomas and Linda. Thank you for teaching me by word and example to pursue personal excellence and for your encouragement, advice, and understanding. Thanks for enjoying my adventures with me.

# CONTENTS

| FIGUR             | ES                                                                                                                                                | V |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---|

| ACKN              | OWLEDGMENTS                                                                                                                                       | i |

| CHAP              | FER 1: Introduction                                                                                                                               | 1 |

| 1.1               |                                                                                                                                                   | 1 |

| 1.2               |                                                                                                                                                   | 4 |

| 1.3               |                                                                                                                                                   | 8 |

| 1.4               |                                                                                                                                                   | 8 |

| 1.5               |                                                                                                                                                   | 9 |

| 1.6               | Introduction to the H Memory                                                                                                                      |   |

| 1.7               | Original Contributions                                                                                                                            |   |

| 1.8               | Thesis Map $\ldots \ldots \ldots$ | 2 |

| CHAP              | FER 2: Today's Memories    13                                                                                                                     | 3 |

| 2.1               | Array Memory                                                                                                                                      |   |

| $2.1 \\ 2.2$      | Volatile Random Access Memory                                                                                                                     |   |

| 2.3               | Volatile Content-Addressable Memory                                                                                                               |   |

| 2.4               | Read-Only Memory                                                                                                                                  |   |

| $\frac{2.1}{2.5}$ | Non-Volatile Memories                                                                                                                             |   |

| 2.6               | Nanotechnology and Nanomemory                                                                                                                     |   |

|                   | 2.6.1 Two and Three Terminal Device Memories                                                                                                      |   |

|                   | 2.6.2 Nano-mechanical Memory                                                                                                                      |   |

|                   | 2.6.3 Silicon Atom Lattice                                                                                                                        |   |

|                   | 2.6.4 Other Non-Silicon Computing Proposals                                                                                                       | ) |

| 2.7               | Summary $\ldots \ldots 43$                                           | 3 |

| СНАР              | ΓER 3: H-Memory Architecture                                                                                                                      | ž |

| 3.1               | Access Method                                                                                                                                     | - |

| $3.1 \\ 3.2$      | Router Macro                                                                                                                                      | - |

| 0.2               | 3.2.1 The "Switch"                                                                                                                                | - |

|                   | 3.2.2 Full Router                                                                                                                                 |   |

| 3.3               | Return Path   51                                                                                                                                  | - |

| 3.4               | Memory Macro                                                                                                                                      |   |

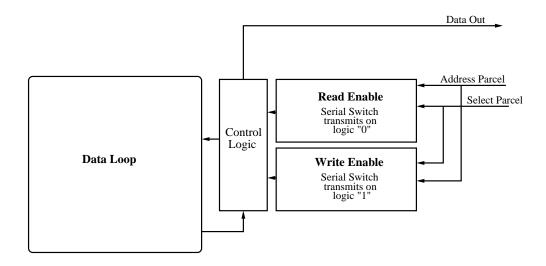

| 0.1               | 3.4.1 Read and Write Enable                                                                                                                       |   |

|                   | 3.4.2 Control                                                                                                                                     |   |

|                                         | 3.4.3 Data Loop                                                                                                                                               |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.5                                     | Conclusion                                                                                                                                                    |

|                                         |                                                                                                                                                               |

|                                         | TER 4: H-Memory Implementation    59                                                                                                                          |

| 4.1                                     | Assumptions                                                                                                                                                   |

| 4.2                                     | Data Loop                                                                                                                                                     |

|                                         | 4.2.1 Parallel Wires Form an Upper Bound                                                                                                                      |

|                                         | 4.2.2 Loop Configurations                                                                                                                                     |

| 4.0                                     | 4.2.3 Closing the Loop $\ldots \ldots \ldots$ |

| 4.3                                     | Macro Implementations                                                                                                                                         |

|                                         | 4.3.1 Memory Macro                                                                                                                                            |

|                                         | 4.3.2 Router Macro $\ldots \ldots \ldots$     |

| 4.4                                     | Comparisons                                                                                                                                                   |

|                                         | $4.4.1  \text{Area Comparison}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                              |

|                                         | 4.4.2 Effect of Brute Force Density Improvements on Latency 76                                                                                                |

|                                         | 4.4.3 Access Time Comparison                                                                                                                                  |

|                                         | 4.4.4 Bandwidth Comparison                                                                                                                                    |

| 4.5                                     | Conclusion                                                                                                                                                    |

|                                         |                                                                                                                                                               |

| СНАРТ                                   | TER 5: Enhancements                                                                                                                                           |

| 5.1                                     | Multi-word leaves                                                                                                                                             |

| $5.1 \\ 5.2$                            | Bouncing Threads Extension                                                                                                                                    |

| 0.2                                     |                                                                                                                                                               |

|                                         |                                                                                                                                                               |

|                                         | 5.2.2 Simulator Description                                                                                                                                   |

|                                         | 5.2.3 Collision Detection and Avoidance                                                                                                                       |

|                                         | 5.2.4 Simulated System                                                                                                                                        |

|                                         | 5.2.5 Benchmark: Bubble Sort $\ldots$                                        |

|                                         | 5.2.6 Results                                                                                                                                                 |

|                                         |                                                                                                                                                               |

| CHAPT                                   | TER 6: Clocking Wire Layout Strategy                                                                                                                          |

| 6.1                                     | Introduction                                                                                                                                                  |

| 6.2                                     | Clocking Wire Density                                                                                                                                         |

| 6.3                                     | Clocking Wire Layout                                                                                                                                          |

| 6.4                                     | Diagonal Clocking Scheme                                                                                                                                      |

| $0.4 \\ 6.5$                            | Evaluating Clocking Strategies                                                                                                                                |

| $\begin{array}{c} 0.5\\ 6.6\end{array}$ | Conclusion $\ldots$                                                          |

| 0.0                                     | 00101051011                                                                                                                                                   |

|                                         |                                                                                                                                                               |

| CHAPT                                   | TER 7: Conclusions and Future Work                                                                                                                            |

# FIGURES

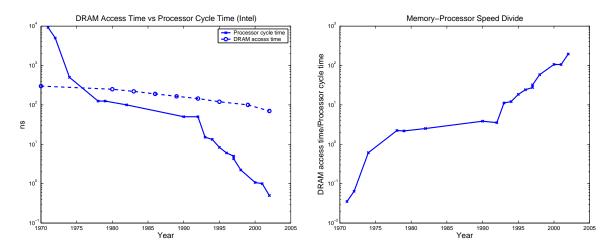

| 1.1 | (a) The gap between DRAM access time and processor cycle times<br>is wide and growing. (b) Moreover, the rate at which the gap is<br>widening is increasing.                                                                                                                                                 | 3  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

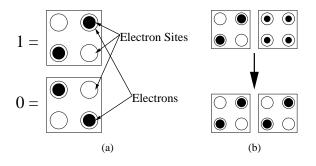

| 1.2 | QCA Cell (a) Polarization and corresponding logic values, (b) Signal propagation in QCA. The cell on the left is polarized, the cell on the right is unpolarized. The cell on the right transitions to assume the polarization of the driving left cell.                                                     | 4  |

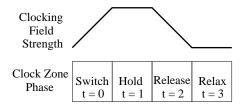

| 1.3 | Propagation of clock signal in a single cell through time                                                                                                                                                                                                                                                    | 5  |

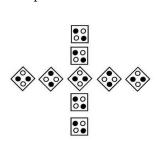

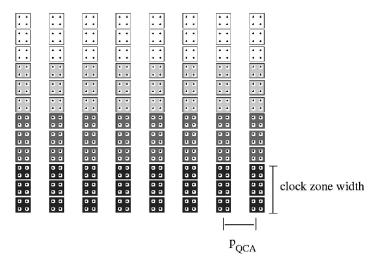

| 1.4 | Shaded boxes indicate clocking zones. a) 90 degree cells forming a "wire". b) 45 degree cells forming a wire                                                                                                                                                                                                 | 6  |

| 1.5 | Wire crossover.                                                                                                                                                                                                                                                                                              | 6  |

| 1.6 | a) Three-input Majority Gate, b) Inverter, c) AND gate d) OR gate .                                                                                                                                                                                                                                          | 7  |

| 1.7 | Example of 90° and 45° wires drawn with QCAD<br>esigner. The shading indicates clock zone. The top wire is a 90° with data moving to the left. The bottom wire is a 45° wire with data moving to the left                                                                                                    | 9  |

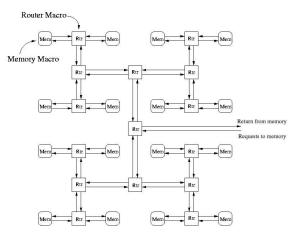

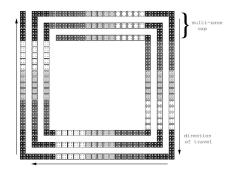

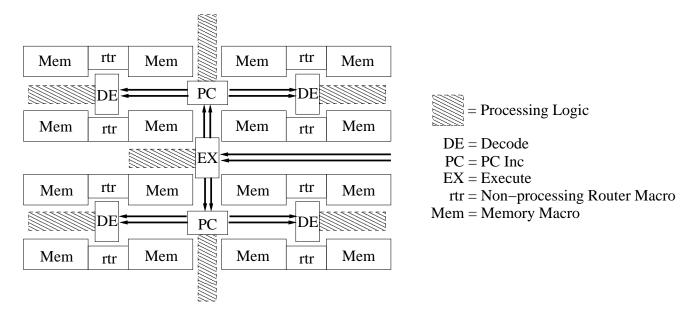

| 1.8 | Basic H-memory Layout showing the organization of memory macros<br>labeled "mem" and router macros labeled "rtr". Accesses enter at<br>the root on the right and travel through the internal router macros<br>to a memory macro leaf, then back through the router macros to the<br>root to exit the memory. | 11 |

| 2.1 | Memory Type Classification                                                                                                                                                                                                                                                                                   | 14 |

| 2.2 | Basic array architecture for 1024x1 configuration, 10 address bits [30]                                                                                                                                                                                                                                      | 16 |

| 2.3 | (a) 6 Transistor SRAM cell. (b) 4 Transistor SRAM cell                                                                                                                                                                                                                                                       | 16 |

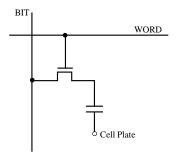

| 2.4 | A one transistor, one capacitor DRAM cell                                                                                                                                                                                                                                                                    | 17 |

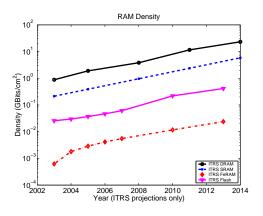

| 2.5 | Density projections for SRAM and DRAM [28]                                                                                                                                                                                                                                                                   | 17 |

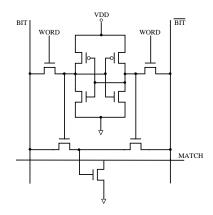

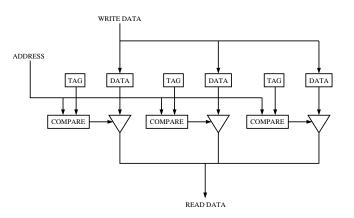

| 2.6 | Content-addressable memory cell [50]                                                                                                                                                                                                                                                                         | 18 |

| 2.7 | CAM architecture for a fast cache [51]                                                                                                                                                                                                                                                                       | 18 |

| 2.8  | Erasable programmable ROM cell and electrically erasable programmable ROM cell [50]                                                                                                                                                                                         | е<br>20 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

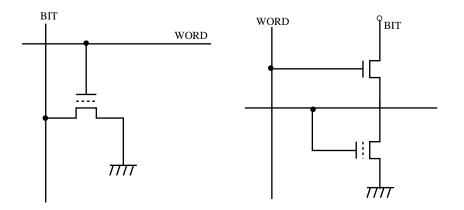

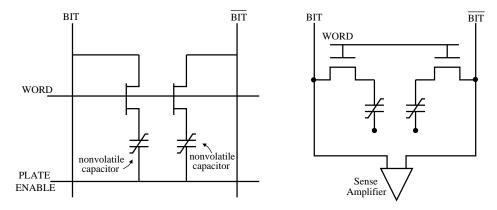

| 2.9  | Two Schematics for two transistor, two capacitor non-volatile ferro-<br>electric RAM cell, without and with sensing scheme. [52]                                                                                                                                            | 22      |

| 2.10 | One transistor, one capacitor non-volatile ferroelectric RAM cells, without and with sensing scheme. [52]                                                                                                                                                                   | 22      |

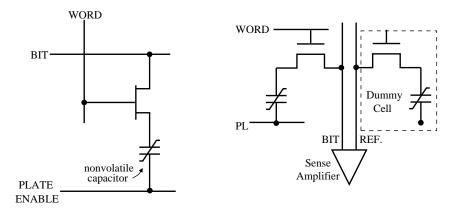

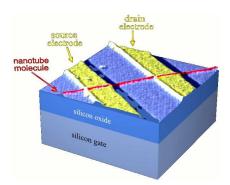

| 2.11 | Schematic for a possible nanotube field effect transistor. $[2]$                                                                                                                                                                                                            | 24      |

| 2.12 | Image of an implementable nanotube FET $[3]$                                                                                                                                                                                                                                | 24      |

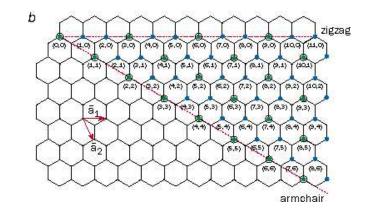

| 2.13 | The chiral vector of nanotubes is defined by $na_1 + ma_2$ , where n and m are integers. Armchair nanotubes have $n = m$ and chiral angle of 30°. Zigzag nanotubes have either n or m equal to zero and chiral angle of 0°. All other nanotubes are considered chiral. [15] | 25      |

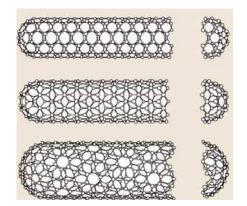

| 2.14 | Three single-walled carbon nanotubes with different chiralities. Pic-<br>tured here is a (5,5) armchair nanotube (top), a (9,0) zigzag nanotube<br>(middle) and a (10,5) chiral nanotube. [15]                                                                              | 25      |

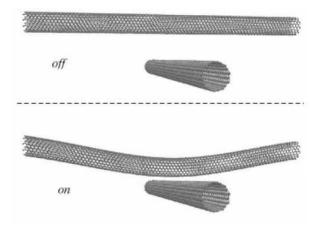

| 2.15 | Nonvolatile nanotube switch in off and on positions $[54]$                                                                                                                                                                                                                  | 27      |

| 2.16 | Overall assembly of Functional Nanoarrays [14]                                                                                                                                                                                                                              | 28      |

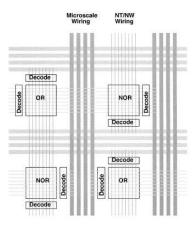

| 2.17 | 8x8 nanoscale array bracketed by decoders and connection to microscale wires. Note that the number of microscale wires grows log-<br>arithmically in array width. For large nanoarrays, the microscale wiring becomes a thin frame around a large nanoscale core. [14]      | 29      |

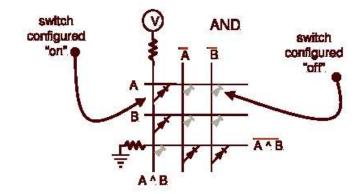

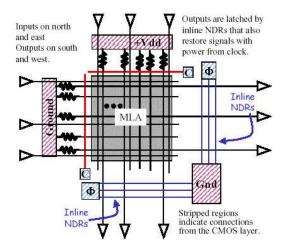

| 2.18 | CAEN implementation of a Two-input AND gate. [23]                                                                                                                                                                                                                           | 30      |

| 2.19 | A schematic of a nanoBlock.[23]                                                                                                                                                                                                                                             | 30      |

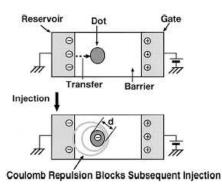

| 2.20 | Schematic view of single-electron box. [63]                                                                                                                                                                                                                                 | 31      |

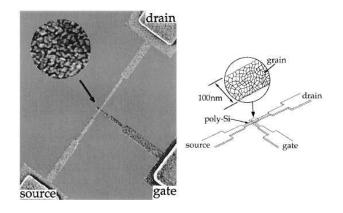

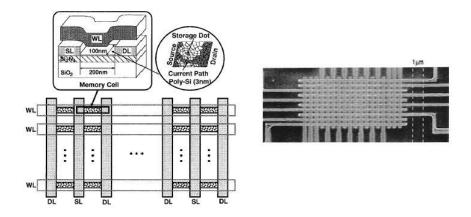

| 2.21 | Memory device formed by sandwiched nanosilicon particles, SEM micrograph and schematic. [63]                                                                                                                                                                                | 31      |

| 2.22 | Overall potential memory architecture, schematic and SEM of micro-<br>scale prototype.[63]                                                                                                                                                                                  | 32      |

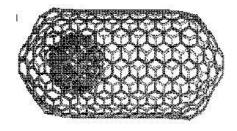

| 2.23 | Structural model for a bucky-shuttle memory element in the logical "0" position. [32]                                                                                                                                                                                       | 33      |

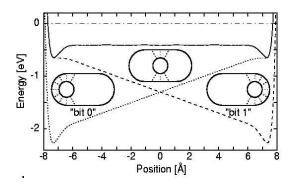

| 2.24 | Potential energy of a particular potential implementation of the bucky-<br>shuttle memory as a function of the shuttle's position compared to<br>the capsule. [32]                                                                                                          | 34      |

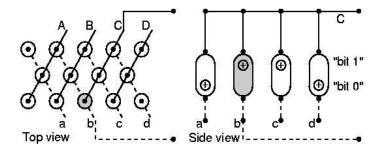

| 2.25 | Schematic of high density memory board. [32]                                                                                                                                                                                                                                | 34      |

|      | Transmission microscope image of multi-walled carbon nanotube that                                                                                                                                                                                                          |         |

| 2.20 | could be used as shuttle memory element.[32]                                                                                                                                                                                                                                | 34      |

| 2.27 | Sample nanomechanical memory devices. a) Interlocking ring cate-<br>nane molecule. b) Dumbbell shaped rotaxane molecule. [1]                                                                                                                                                                       | 36 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.28 | Possible tilable device architecures. (a) Three terminal device in a hexagonal lattice, where G signifies the gate, S the source, and D the drain. M represents a molecule. (b) A two terminal device used in a cross-bar architecture. [49]                                                       | 37 |

| 2.29 | Fabrication of two-terminal molecular (catenane) switch. (a) Smooth silicon substrate. (b) Parallel etched polysilicon wires. (c) Deposition of catenane monolayer. (d) Second layer of wires perpendicular to the original wires, formed by condensing titanium vapor through a shadow mask. [49] | 37 |

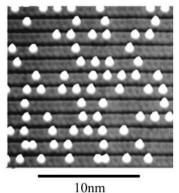

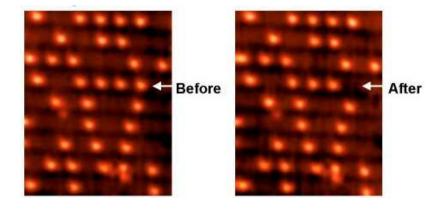

| 2.30 | Silicon atomic lattice. Horizontal lines are gold tracks exactly five atoms wide (1.7 nm). White circles are a single silicon atom representing a bit. Along the tracks, the silicon atoms are seperated by 4 atom-widths. [7]                                                                     | 38 |

| 2.31 | Writing a "zero" involves physically removing the cluster of silicon atoms using a scanning tunneling microscope. [7]                                                                                                                                                                              | 39 |

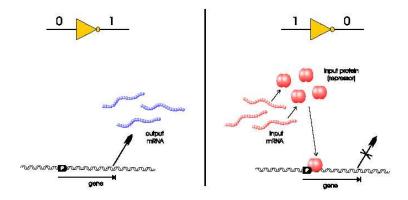

| 2.32 | Simplified genetic inverter. On the left, the input is a logical "0", allowing the gene to be expressed, producing mRNA output (a logical "1"). On the right, a mRNA is presented to the system (logical "1") which represses the production of the output mRNA (logical "0"). [62]                | 42 |

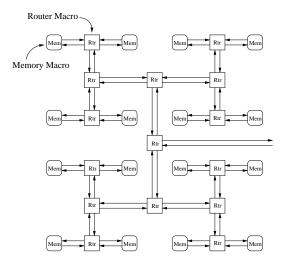

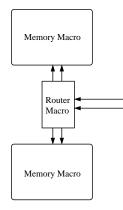

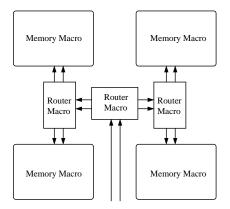

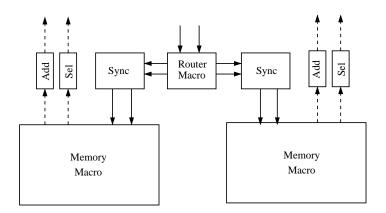

| 3.1  | Basic H-memory Layout showing the organization of memory macros labeled "mem" and router macros labeled "rtr"                                                                                                                                                                                      | 46 |

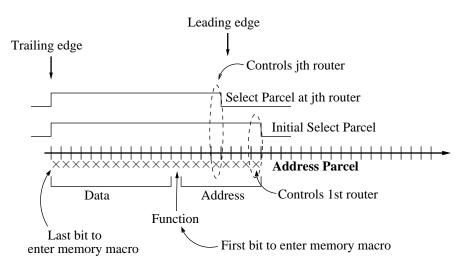

| 3.2  | Change in parcels for an H-memory (12 bits/word, 256 word) as the parcels travel toward memory macro. At each router, the leading bit of the select parcel is stripped away                                                                                                                        | 47 |

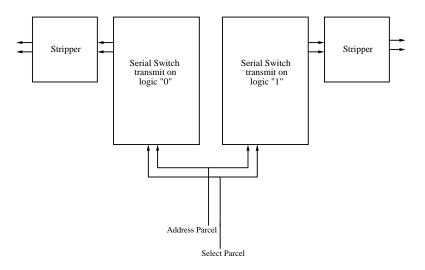

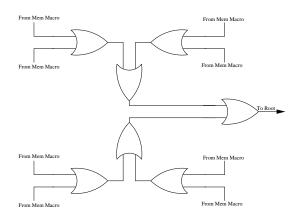

| 3.3  | Components of a router macro. The serial switch modules selectively transmit the select parcel. The "stripper" module strips the leading bit from the select parcel after transmission.                                                                                                            | 48 |

| 3.4  | A single H at the lowest level of the tree shows a router macro connecting two memory macros. This figure shows the down-tree wires                                                                                                                                                                | 50 |

| 3.5  | New router macro connecting two smaller Hs                                                                                                                                                                                                                                                         | 51 |

| 3.6  | The return routers are OR gates whose inputs combine to return the data to the root of the memory.                                                                                                                                                                                                 | 52 |

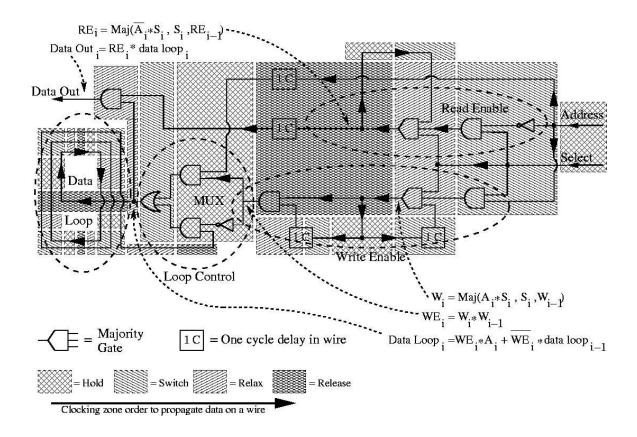

| 3.7  | Components of a memory macro: two serial switches, the data loop, and minimal additional control logic that executes the read and write operations.                                                                                                                                                | 52 |

|      |                                                                                                                                                                                                                                                                                                    |    |

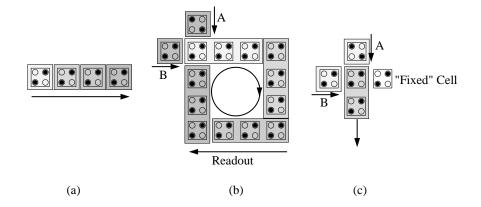

| 3.8  | Three basic QCA memory cells. a) Translation of DRAM, b) Translation of SRAM. When A=B, a new value is written to the cell. $A \neq B$ , the previously stored value remains. c) ROM cell. If A=B, that value is output. If A $\neq$ B, the stored value is read out. [31]                                                                                                                                               | 55 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Spiral data loop storing 14 bits that circulate in a clockwise direction.<br>Here, the ends of the loop are shown to join together directly without<br>intermediate control logic. The turns of the spiral are made of 90<br>degree wires. The segment of wire closing the loop is a 45 degree wire,<br>allowing the signals to cross over eachother without interference. Cell<br>shading indicates the clocking zones. | 56 |

| 3.10 | Cascaded data loops allowing arbitrary numbers of bits to be stored<br>in a single wire                                                                                                                                                                                                                                                                                                                                  | 57 |

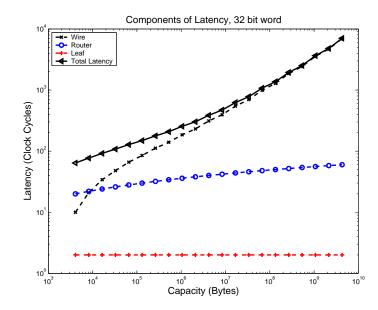

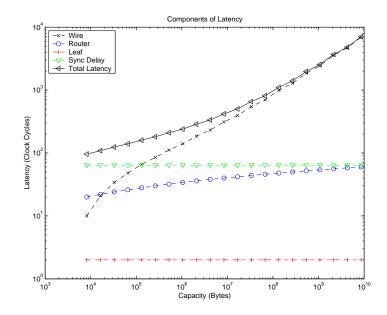

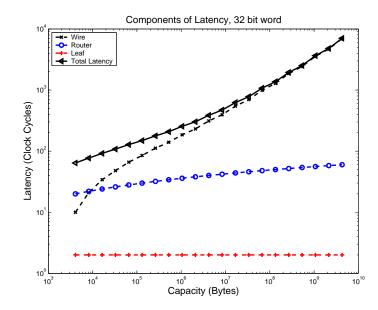

| 4.1  | Components of latency as the memory capacity grows for a 32 bit word and a varying number of memory macros.                                                                                                                                                                                                                                                                                                              | 60 |

| 4.2  | Given an area and a minimum clock zone size, an upper bound on<br>the capacity of a storage loop can be identified.                                                                                                                                                                                                                                                                                                      | 63 |

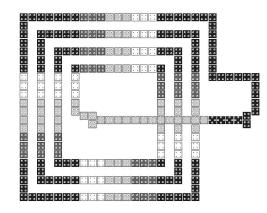

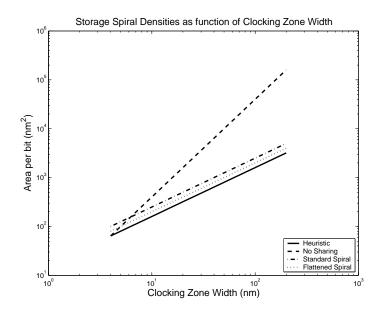

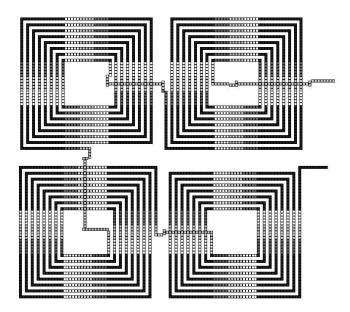

| 4.3  | The flattened spiral configuration for a data loop drawn with a 5x5 cell minimum clocking zone, and a 1 cell minimum wire separation. There is at least one bit stored on each not cap side per turn. The cap zones consist of one zone, the size of which is constrained by the longest wire passing through it (i.e. the outside turn of the spiral)                                                                   | 66 |

| 4.4  | The standard spiral configuration for a data loop drawn with a 5x5 cell minimum clocking zone, and a 1 cell minimum wire separation. There is one bit stored on each side per turn                                                                                                                                                                                                                                       | 66 |

| 4.5  | Area required per bit for the heuristic, no clocking zone sharing and<br>two spiral configurations as a function of clocking zone width. As the<br>size of the clocking zone grows, the benefit of sharing clocking zones<br>for multiple bits increases.                                                                                                                                                                | 67 |

| 4.6  | Memory macro layout. See figure 4.7 for schematic and boolean equa-<br>tions describing memory macro operation.                                                                                                                                                                                                                                                                                                          | 69 |

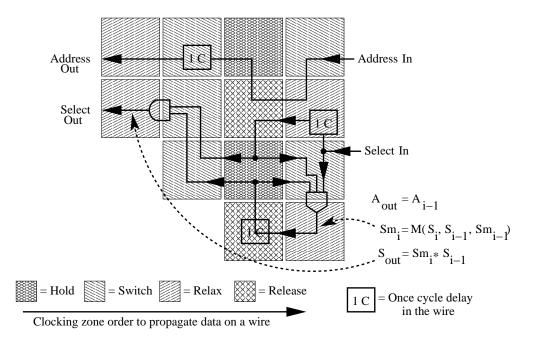

| 4.7  | Memory macro schematic. Shaded areas indicate clocking zone. Once<br>a wire crosses a clocking zone boundary, its data is effectively latched.                                                                                                                                                                                                                                                                           | 70 |

| 4.8  | Data loop containing more than 32 bits                                                                                                                                                                                                                                                                                                                                                                                   | 72 |

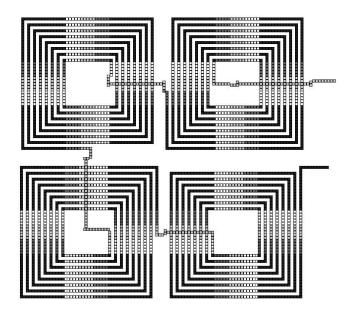

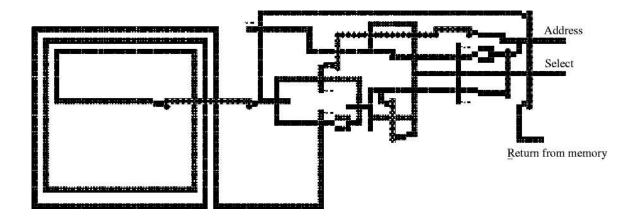

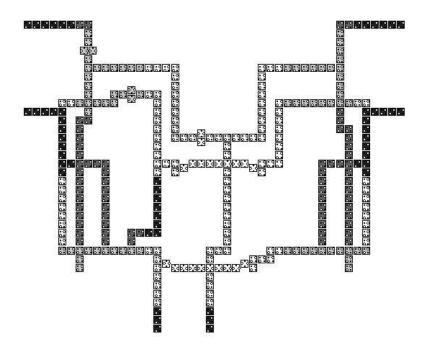

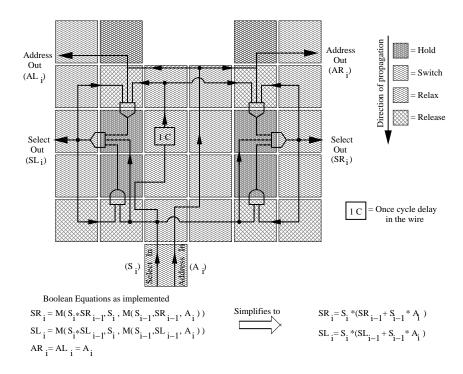

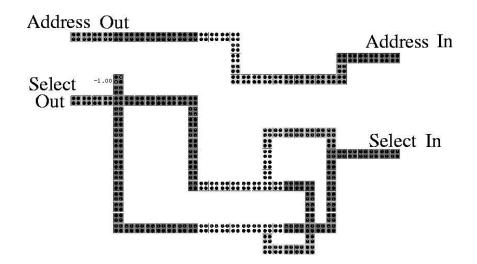

| 4.9  | Router macro layout.See figure 4.10 for schematic                                                                                                                                                                                                                                                                                                                                                                        | 73 |

| 4.10 | Router macro schematic. The shaded areas represent clocking zones.<br>Once a wire crosses a clocking zone boundary, its data is effectively<br>latched.                                                                                                                                                                                                                                                                  | 74 |

| 4.11 | Stripper macro layout for removing the leading edge of the select parcel. See figure 4.12 for schematic.                                                                                                                                                                                                                                                                                                                 | 74 |

| 4.12 | Stripper macro schematic. Shaded areas indicate clocking zone. If a wire crosses a clocking zone boundary, it's data is effectively latched.                                                                                                                                                                                                      | 75 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

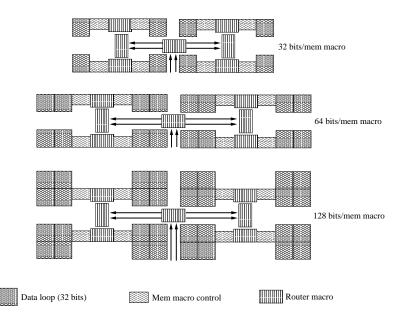

| 4.13 | Memory macros and router macros shown in correct relative size for<br>three data loop capacities. As the number of bits stored per memory<br>macro grows, the size of the memory macro grows while the size of<br>the router macro stays constant                                                                                                 | 76 |

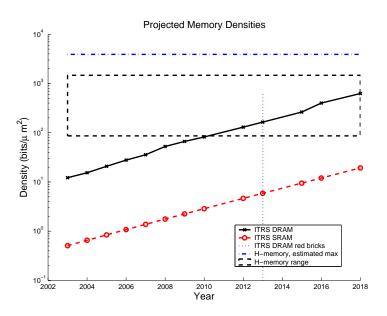

| 4.14 | Density comparison between basic H-memory and ITRS projections<br>for SRAM and DRAM. A range of H-memory densities for 1G of<br>memory macros with between 32 and 1024 bits per word is shown.<br>The maximum estimated H-memory density uses an 8x8 cell clock<br>zone and the 2.0 nm cell. The ITRS "red brick wall" for DRAM is<br>also shown. | 77 |

| 4.15 | Components of latency as the memory capacity grows.                                                                                                                                                                                                                                                                                               | 79 |

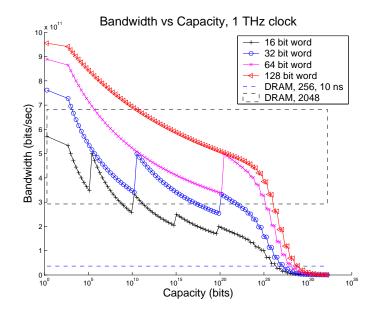

| 4.16 | Bandwidth of the basic H-memory configuration for varying capaci-<br>ties and two estimates for DRAM bandwidth. The DRAM estimates<br>assume 1/3 open row hit probability, a 1 ns open row access time,<br>and a 10 ns random access time                                                                                                         | 81 |

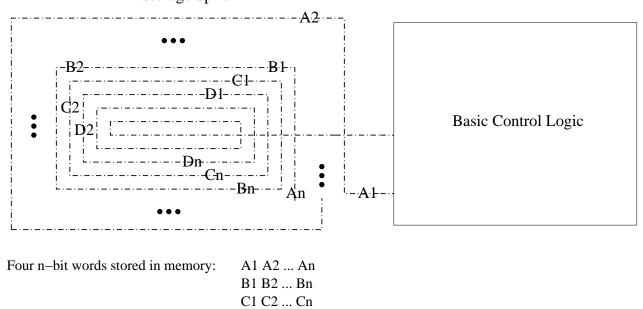

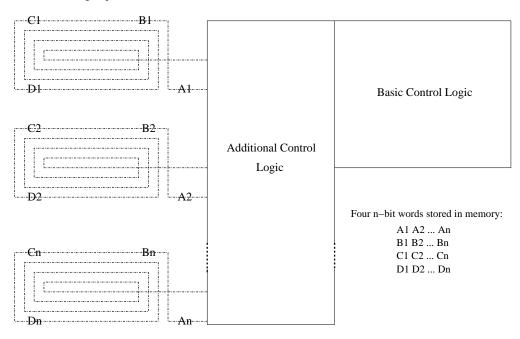

| 5.1  | Alternative memory macro configuration to store multiple words in a single memory macro spiral. Maximum synchronization delay is the total number of bits in the spiral $(n_w * w_l)$ .                                                                                                                                                           | 86 |

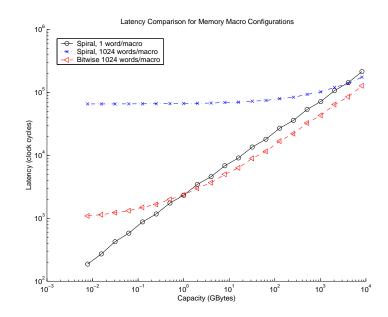

| 5.2  | Components of latency as the memory capacity grows, 32 bits per memory macro.                                                                                                                                                                                                                                                                     | 87 |

| 5.3  | Worst case latency incurred for three memory macro configurations                                                                                                                                                                                                                                                                                 | 88 |

| 5.4  | Alternative memory macro configuration based on bubble memory<br>design to efficiently access one of multiple words stored in a single<br>memory macro. Maximum synchronization delay is the number of<br>words stored in the memory macro                                                                                                        | 89 |

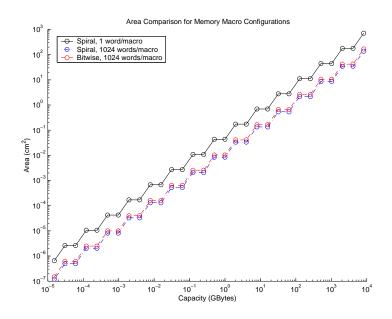

| 5.5  | Area requirements for three memory macro configurations                                                                                                                                                                                                                                                                                           | 90 |

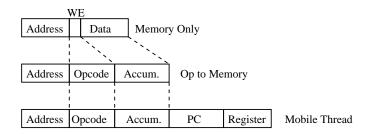

| 5.6  | Fields for memory access, operations to memory, and independent thread [53]                                                                                                                                                                                                                                                                       | 90 |

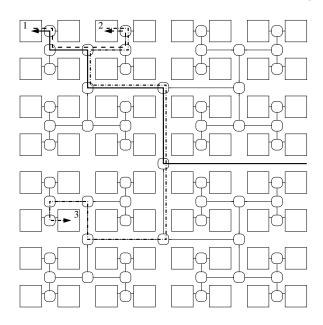

| 5.7  | Sample processing router pipeline placement for bouncing threads<br>execution model. Pipeline stages include iFetch (occurs at memory<br>macros), program counter increment, decode, and execute. In this<br>example, the lowest level routers are non-processing router macros.<br>[21]                                                          | 91 |

| 5.8  | Threads travel between memory macros without returning to the root<br>in the bouncing threads model. In this example, threads travel first<br>to the memory macro marked "1", then to "2" and finally to "3"<br>without returning to the root.                                                                                                    | 92 |

|      |                                                                                                                                                                                                                                                                                                                                                   |    |

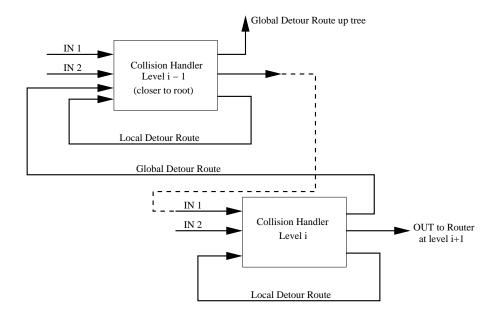

| 5.9  | Collisions occur when two or more threads are trying to use the same output path at the same time                                                                                                                                                | 95 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

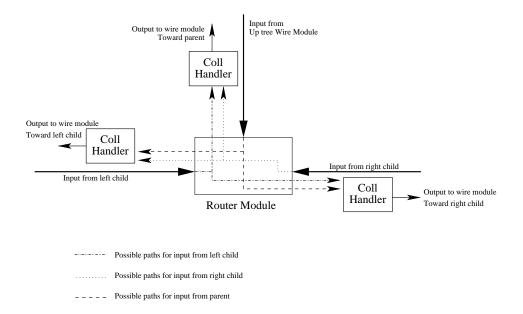

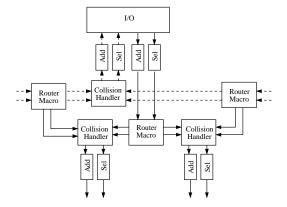

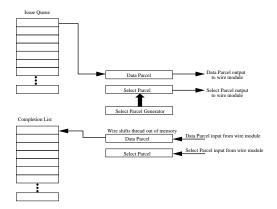

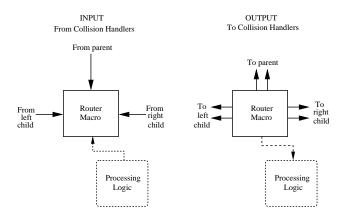

| 5.10 | Simulator module interaction at I/O module and internal nodes<br>Solid lines signify wire modules that represent down-tree connections.<br>Dashed lines are wire modules that represent up-tree connections                                      | 96 |

| 5.11 | Simulator module interaction at memory macros. Solid lines signify<br>wire modules that represent down-tree connections. Dashed lines are<br>wire modules that represent up-tree connections                                                     | 97 |

| 5.12 | I/O module handles the initial issue of a thread into the H-tree and the final notification of a process's completion.                                                                                                                           | 97 |

| 5.13 | Creating detour routes in collision handlers increases the number of<br>threads that can be involved in a single collision and increases the<br>types of collisions that can occur. a) local detour route, b) global<br>detour route             | 99 |

| 5.14 | The wire module explicitly represents each transitory latch in the wire. Each update cycle, contents of the wire are shifted forward by one position. This wire spans a distance that requires four clock cycles to traverse                     | 00 |

| 5.15 | Router module is responsible for sending the thread toward the appropriate memory macro. It may or may not include processing logic. 10                                                                                                          | 00 |

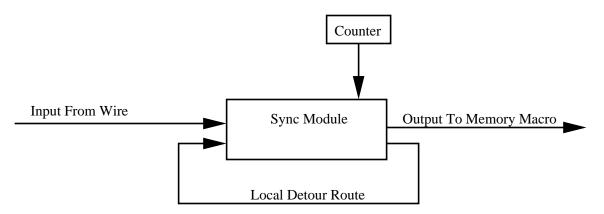

| 5.16 | The sync module guarantees the thread enters the memory macro to correspond to the start of the word stored in the memory macro. The sync module also handles collisions that arise from multiple threads trying to access the same memory macro | 01 |

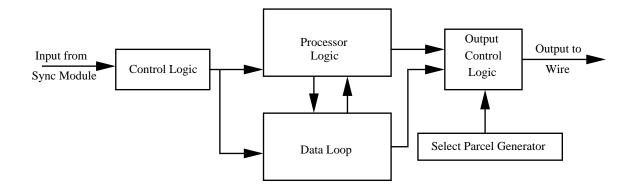

| 5.17 | The memory module models the memory macros. Each memory macro has a word of storage and may include a serial processor 10                                                                                                                        | 02 |

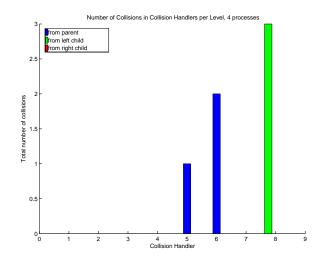

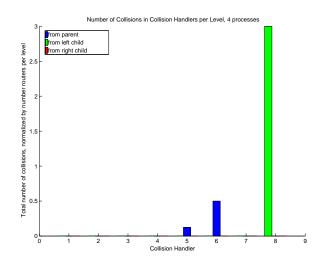

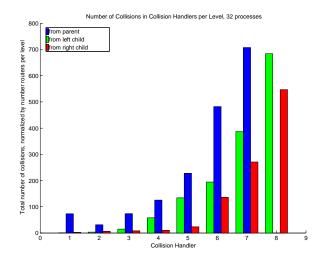

| 5.18 | Total number of collisions at each level for 4 processes in the memory structure. Level 1 is closest to the memory macros and includes 128 collision handlers. Level 8 is at the root with one collision handler 10                              | 04 |

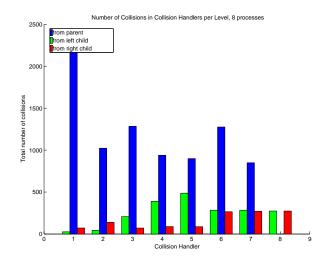

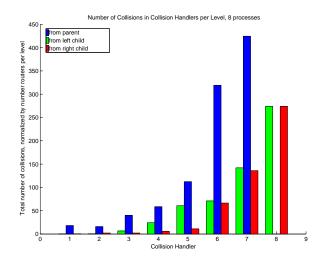

| 5.19 | Total number of collisions at each level for 8 processes in the memory structure. Level 1 is closest to the memory macros and includes 128 collision handlers. Level 8 is at the root with one collision handler 10                              | 05 |

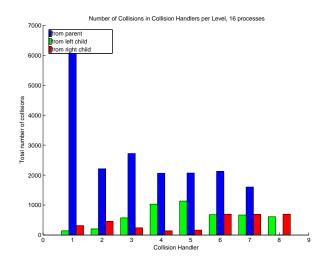

| 5.20 | Total number of collisions at each level for 16 processes in the memory structure. Level 1 is closest to the memory macros and includes 128 collision handlers. Level 8 is at the root with one collision handler 10                             | 05 |

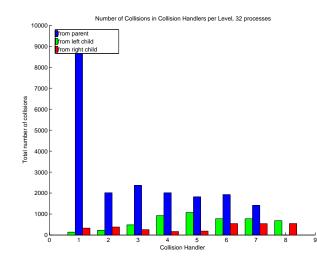

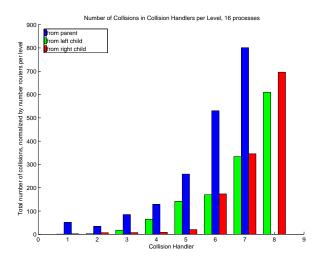

| 5.21 | Total number of collisions at each level for 32 processes in the memory structure. Level 1 is closest to the memory macros and includes 128 collision handlers. Level 8 is at the root with one collision handler 10                             | 06 |

|      |                                                                                                                                                                                                                                                  |    |

| 5.22 | 2 Number of collisions at each level for 4 processes in the memory<br>structure normalized by the number of collision handlers at each level.<br>Level 1 is closest to the memory macros and includes 128 collision<br>handlers. Level 8 is at the root and has one collision handler                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.23 | <sup>3</sup> Number of collisions at each level for 8 processes in the memory<br>structure normalized by the number of collision handlers at each level.<br>Level 1 is closest to the memory macros and includes 128 collision<br>handlers. Level 8 is at the root and has one collision handler                            |

| 5.24 | Number of collisions at each level for 16 processes in the memory<br>structure normalized by the number of collision handlers at each level.<br>Level 1 is closest to the memory macros and includes 128 collision<br>handlers. Level 8 is at the root and has one collision handler 107                                    |

| 5.28 | 5 Number of collisions at each level for 32 processes in the memory<br>structure normalized by the number of collision handlers at each level.<br>Level 1 is closest to the memory macros and includes 128 collision<br>handlers. Level 8 is at the root and has one collision handler 108                                  |

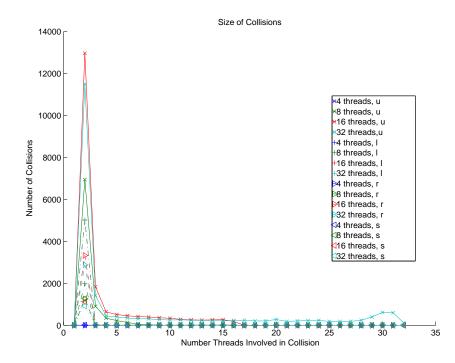

| 5.20 | Frequency of collisions of each size depending on the number of pro-<br>cesses in the memory structure. Regardless of the number of threads<br>executing, most threads involve 3 threads or less. However, with $n$<br>threads executing, there are a few collisions with as many as $n$ threads<br>involved                |

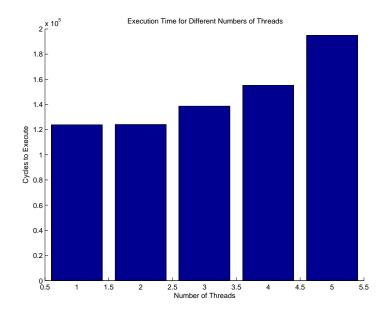

| 5.2' | <sup>7</sup> Execution time for all processes depending on how many processes<br>are executing simultaneously                                                                                                                                                                                                               |

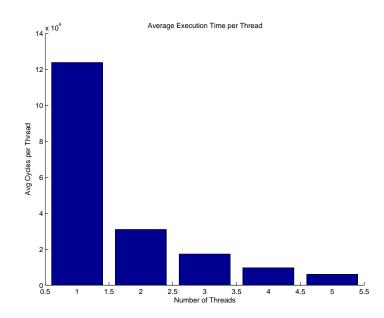

| 5.28 | Average execution time for different numbers of processes executing simultaneously.                                                                                                                                                                                                                                         |

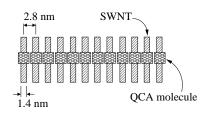

| 6.1  | The size of SWNTs is on the same size scale as molecular QCA cells.<br>Clocking wires made of SWNTs may not limit the density of QCA circuits. The diameter of the $(10,10)$ SWNT is $1.4nm$ . The center to center distance between QCA molecules is $2.8nm$                                                               |

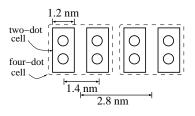

| 6.2  | Cell to cell distance of a four dot QCA cell built from two 2-dot molecules                                                                                                                                                                                                                                                 |

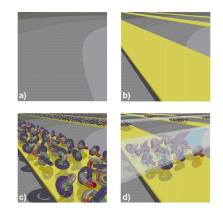

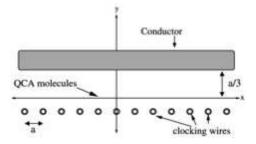

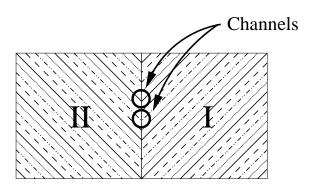

| 6.3  | Schematic of clocking wires below the plane of a QCA circuit. Clock-<br>ing wires run perpendicularly out of the viewing surface. QCA cells<br>are placed on the plane sandwiched between the clocking wires and<br>an upper conducting plate. [26]                                                                         |

| 6.4  | Electric field generated by CMOS wires placed under the plane of<br>the QCA molecules. Block dots are the CMOS wires which run per-<br>pendicular to the viewing plane. The layer where QCA molecules<br>reside is located at the horizontal 0 line. The highest black line is the<br>conductor as seen in figure 6.3. [26] |

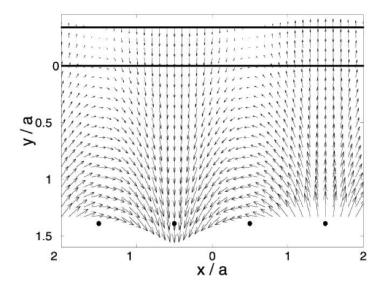

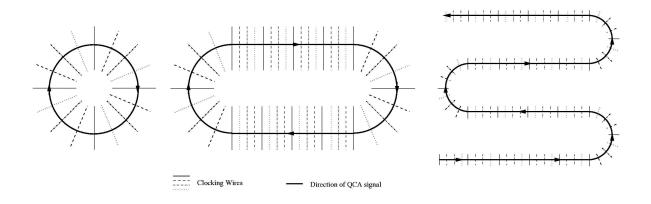

| 6. | Three clocking wire layouts: (a) Straight QCA signal traveling per-<br>pendicular to the clocking wires. (b) QCA turn with perpendicular<br>wires. (c) QCA signal traveling at 45 degree angle to clocking wires.                                                                                                       | . 115 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

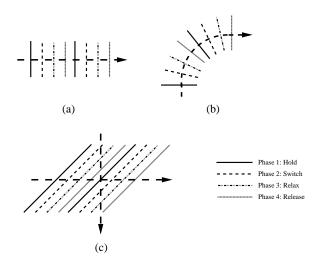

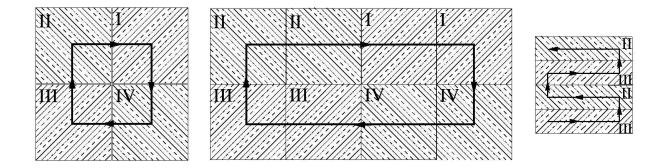

| 6. | I-IV Diagonal wire layout metazones. a-d) Supported direction of movement of overlying QCA signals.                                                                                                                                                                                                                     | . 117 |

| 6. | Channels between two meta-zones. For the four phase clock scheme, channels occur every other clocking wire along the border between two meta-zones.                                                                                                                                                                     | . 117 |

| 6. | Three loop configurations with the perpendicular clocking wire layout<br>strategy. The configurations are the standard spiral, the flattened<br>spiral, and the snake configuration. The bold line shows the direction<br>of the overlying QCA signal. The patterned lines indicate the relative<br>phase of each wire. | . 119 |

| 6. | Three loop configurations with the diagonal clocking wire layout<br>strategy. The configurations are the standard spiral, the flattened<br>spiral, and the snake configuration. The bold line shows the direc-<br>tion of the overlying QCA signal. The patterned lines indicate the<br>relative phase of each wire     | . 119 |

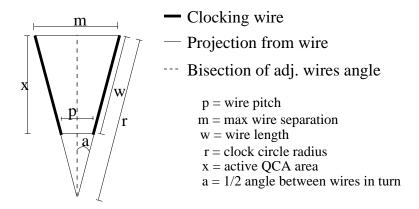

| 6. | 0 Parameters used to calculate clocking wire density on a turn for the perpendicular clocking wire layout.                                                                                                                                                                                                              | . 123 |

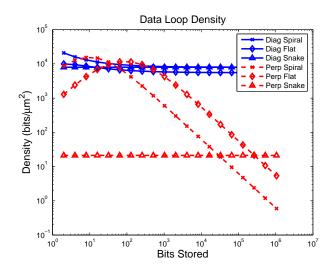

| 6. | 1 Density of data loops using the perpendicular clocking wire layout<br>scheme and the diagonal clocking wire layout scheme for different<br>QCA wire widths. The clocking wire pitch is limited by the size of<br>the QCA pitch. Uses parameters in table 3                                                            | . 123 |

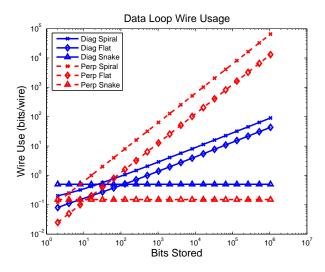

| 6. | 2 Clocking wire usage by data loops using the perpendicular clocking wire layout scheme and the diagonal clocking wire layout scheme for different QCA wire widths                                                                                                                                                      | . 124 |

## ACKNOWLEDGMENTS

I would like to especially thank my advisor, Dr. Peter Kogge, for guiding me onto a path of valuable and fun research, for providing incredible opportunities to learn and grow as a person and a researcher, and for allowing me to pursue a few detours that were more valuable and horizon broadening than I can ever say.

I would also like to thank my committee, Dr. Eugene Henry and Dr. Sharon Hu for their valuable contribution to this endeavor.

Many thanks also go to Dr. Craig Lent, Mike Niemier, and Arun Rodrigues for valuable discussions about the nature of QCA and for turning the task of designing with QCA from looking like a snarling, angry bear to a good natured puppy. A particular thanks to Dr. Megan Frost for explaining to this non-chemist the chemistry and principles of how the molecular world works. Thank you to Megan, Mike, and Arun for showing by example what grad school and research are all about.

A very special thanks to Richard Murphy for being a valuable sounding board, giving invaluable advice and encouragement, and keeping me as sane as possible during this pursuit.

Finally, I would like to thank the Semiconductor Research Corporation (SRC) and the Clare Boothe Luce Foundation for supporting this work.

# CHAPTER 1

## Introduction

#### 1.1 The Problem

The goal of computer designers and manufacturers is to produce smaller, faster computers. In 1965, Gordon Moore described the success of the industry in this matter noting that between 1959 and 1965, the number of components on a die grew exponentially [37]. This trend has continued with the number of transistors on a die nearly doubling every 18-24 months. This success has been achieved primarily by shrinking the size of the transistor, aided by the increasing size of the die. For instance, Intel's 4004 released in 1971 was made of 2300, 10 micron transistors on a 12  $mm^2$  die [57]. In contrast, today's chips contain tens or hundreds of millions of transistors near 0.07 microns on dies on the order of several hundred square millimeters.

However, the current strategy of shrinking the transistors and maintaining the same design paradigm will soon be insufficient to meet physical, economic, and architectural barriers. The smallest transistors in production today operate despite quantum effects. In the near future, the operation of transistors will be dominated by the quantum world. The current device, the CMOS transistor, will need to be replaced by one that embraces these quantum effects and takes advantage of the physics that governs at the nano-scale. Fabrication costs, short lifetime of chip generations, rising capital costs, and demand for computing power from consumers all create economic challenges for the semiconductor industry [55]. Finally, as the gap between processor and memory speeds continues to grow, the von Neumann bottleneck will create a greater and greater architectural barrier to continued performance increases.

In addition to these general comments, memory architecture in particular needs to be reexamined for two reasons. First, the gap between memory access times and processor cycle times is large and growing faster (figure 1.1). Most recent architectural advancements in processor architecture are aimed at masking the memory access latency. As the relative divide between memory access time and processor cycle time grows, it will become more and more difficult for processor architectures to mask this latency. Rather than attempting to mask this latency, it is time to address memory architecture to reduce the latency itself.

Second, the transistor paradigm will have particular trouble in memory at the nanoscale. As transistors are scaled down in size, the leakage current increases. This is a particular problem for memory cells. Leakage current translates to heat generation which limits the density of storage. If memory cells are too close together, the heat generated could destabilize the cells (e.g. flip a stored zero to a one). This constraint will negatively impact the memory density of CMOS memory at the nanoscale.

Finally, the array architecture does not translate well to the nanoscale due to an increase in both transient and permanent errors. Transient faults will be more common because the energies at which bits are stored will be lower than current memories and will therefore be more susceptible to fluctuations due to doping problems both at fabrication time and during use caused by electromigration of atoms during memory operation. Bits will also be more susceptible to high energy particles which cause energy spikes that could flip stored bits. Permanent errors will also be more common because of the difficulty of fabrication at the nanoscale. While massive redundancy could address the permanent errors as the extra rows in today's array memories, the array structure would be particularly susceptible to transient errors that could make entire rows or columns unpredictably inaccessible. In addition, this sort of massive redundancy would have a significant impact on the density of the memory.

There are several groups exploring nanotechnology answers to the memory problem. These nanotechnology devices and proposed array architectures will be discussed in chapter 2.

Figure 1.1. (a) The gap between DRAM access time and processor cycle times is wide and growing. (b) Moreover, the rate at which the gap is widening is increasing.

These barriers point to the need for a new kind of fundamental device and architecture, such as quantum-dot cellular automata (QCA). The device characteristics of QCA, which will be introduced below, are quite different from CMOS characteristics. This changes the cost landscape which in turn changes the look of efficient designs. The design framework presented in this thesis takes advantage of the characteristics of QCA as well as offering an option for alleviating or eliminating the von Neumann bottleneck.

#### 1.2 An Architect's Introduction to Quantum-dot Cellular Automata

Quantum-dot cellular automata (QCA) is a novel alternative to the transistors, silicon, and CMOS paradigm. Rather than using charge movement, current, to propagate signals and perform operations, QCA uses devices as charge holders, using Coulombic repulsion of electrons as the primary computing force. A QCA cell consists of four quantum dots arranged in a square with two excess electrons that can occupy the dots. Because the electrons are repelled by each other, they naturally reside in opposite corners. As a result, the cell has two stable states. The first is an electron in the bottom left corner and the top right corner. A cell with this configuration has a polarization of +1 and represents logical "1". The second stable state is an electron in the top left corner and the bottom right corner, a polarization of -1 representing a logical 0 (figure 1.2). The electrons can tunnel between the quantum dots allowing them to change configurations.

Figure 1.2. QCA Cell (a) Polarization and corresponding logic values, (b) Signal propagation in QCA. The cell on the left is polarized, the cell on the right is unpolarized. The cell on the right transitions to assume the polarization of the driving left cell.

Computation is performed by controlling the tunneling with a four phase "clock"

signal (figure 1.3). Unlike CMOS circuits, the QCA clock is a fundamentally different phenomenon than the data. The clock raises and lowers the barriers between the dots, alternately prohibiting and allowing the electrons to tunnel between dots. The raising and lowering behavior of the clock signal is described by four phases called switch, hold, release, and relax. In the switch phase, the barriers begin low, allowing tunneling, and are raised to prohibit tunneling. In this phase, the cell transitions from having no value to having a definite value. The hold phase follows switch in which the barriers are maintained high, preserving the value assumed during switch. In the release phase, the barriers are falling, allowing the cell to go from a well-defined state to an undefined state in which the cell has no natural polarization. Finally, the relax phase maintains low barriers and no polarization.

Figure 1.3. Propagation of clock signal in a single cell through time.

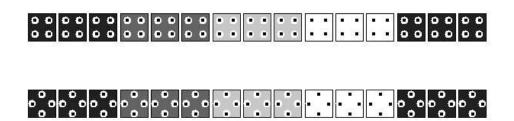

If QCA cells are lined up side by side and clocked appropriately, they act as a wire, propagating a signal down its length (figure 1.4a). Cells laid out in this side by side manner are called 90 degree cells. The alternative is 45 degree cells which are laid out corner to corner (figure 1.4b). In a 45 degree wire, the signal is inverted at each cell. If the first cell holds a "1", the second cell will hold a "0", followed by a "1" in the third cell, and so on.

QCA cells exist on a single plane. The two types of wires are able to crossover each other in this single plane without effecting the values being transmitted (figure

Figure 1.4. Shaded boxes indicate clocking zones. a) 90 degree cells forming a "wire". b) 45 degree cells forming a wire.

1.5). This makes complex circuits possible.

Figure 1.5. Wire crossover.

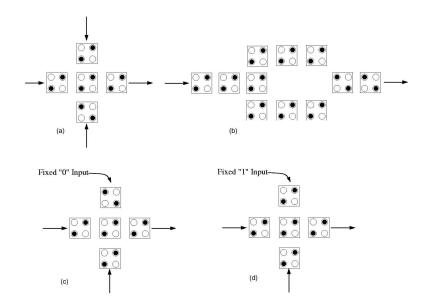

The basic logic gate in QCA is the three input majority gate (figure 1.6a). Three input cells are arranged on the edges of a center "device cell." The output of the gate is on the fourth edge of the device cell. The input cells and the device cell share the same clock zone. Because of this and simple coulombic repulsion, the device cell assumes the value of the majority of the inputs. When this device cell is frozen in the hold phase, it drives the output cell which then proceeds as a normal QCA wire. It is notable that the majority gate is a natural, native device in QCA. It requires nothing more than the QCA cells and clocking already introduced. This majority gate can be converted to either an AND gate or an OR gate by fixing one of the inputs to be permanently "0" (figure 1.6c) or "1" (figure 1.6d) respectively.

Figure 1.6. a) Three-input Majority Gate, b) Inverter, c) AND gate d) OR gate

An inverter is needed for logical completeness, and is formed by taking advantage of the 45 degree interaction (figure 1.6b).

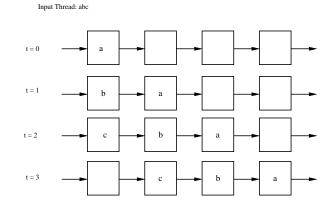

In addition to these basic gates, the design landscape also includes three other important features. The first is the inherent latching in wires. In essence, the wires are shift registers. This adds a new dimension to designing QCA circuits rather than CMOS circuits, allowing a designer to pipeline at a very fine level. Connected to this inherent latching and pipelining, the second feature of QCA is the close connection between layout and timing [47]. There is an upper and lower bound on the size of clocking zones. Distances and time, then, are very tightly coupled. Finally, bits in QCA designs are always in motion. The clock and the cells are made of different technologies. Perhaps in the future it may be feasible to have the circuit influence the operation of the clock, but for the designs presented in this thesis, it is assumed that once the clock starts running, it continues to operate independently of the circuit. This, too, changes the design decisions made.

### 1.3 Prior QCA Architecture Work

Computer engineering QCA research first focused on device basic logical devices and an adder as an example of a QCA circuit [58]. Niemier's work was the first look at the effect QCA has on architecture and system design. His initial work focused on the hand designing of a simple but complete processor in QCA much as the first Intel 8086 processor was designed [39][4]. In the course of this work, Niemier identified several key elements of circuit design in QCA including the connection between layout and timing [47], the potential of processing-in-wire and fine-grained pipelining [46] [43] [42] [41], and initial floorplanning for logic [39]. In addition, since the first molecular QCA circuits that will be fabricated will need to be regular structures, the design of implementable FPGAs was explored [45] [44]. Another key work explored the layout parameters and layout rules that will govern the layout of QCA circuits [40].

Niemier's work identified key issues in the design of QCA logic circuits and systems. The principles he identified apply to memory as well as logic, but memory has a different set of important requirements.

Research is also being pursued to build fault models for QCA circuits in order to build fault tolerant circuits and to build CAD tools to facilitate testing and design of circuits [16]. In addition, the first algorithm that addresses the circuit partitioning problem in QCA has been developed [6].

## 1.4 Note on Circuit Figures

The circuit figures in this work require a brief comment. Most of the QCA figures presented in this work are drawn using a tool called QCADesigner [60]. The shadings

of the cells indicate their clocking zone. For instance, figure 1.7 illustrates two wires with data propagating to the left. In this example, each clocking zone has three cells per wire in it. The top wire is a 90° wire, while the bottom wire is a 45° wire. Each wire passes through five clocking zones. The first four correspond to switch, hold, release, and relax respectively. The last clocking zone begins to repeat the pattern and is in switch. It is important to note, also, that unlike the figures presented previously, the cells in these figures are merely place holders and do not represent the polarization of each cell.

Figure 1.7. Example of  $90^{\circ}$  and  $45^{\circ}$  wires drawn with QCAD esigner. The shading indicates clock zone. The top wire is a  $90^{\circ}$  with data moving to the left. The bottom wire is a  $45^{\circ}$  wire with data moving to the left.

#### 1.5 The Real Device

QCA is very real. QCA cells have been fabricated and their operation experimentally verified [8] [48]. These QCA cells were constructed with metal dots on a micron scale and operate at 70 mK. As the size of the cell grows smaller, the operational temperature will rise [33]. A molecular implementation, then, would allow room temperature operation as well as offering significant potential density gains in circuits. Lieberman, *et al* have investigated several two dot-molecules such as the Creutz-Taube ion and mixed-valence ruthenium dimers. In addition, they have explored options for attaching these molecules to etched self-assembled monolayers [36]. Other groups at Notre Dame are investigating four-dot molecules[35] and alternate fabrication strategies such as DNA tiling.

In addition to the QCA cells, a functioning QCA circuit requires a clock signal and input/output capabilities. Lent, *et al* have designed an implementable clocking scheme in which buried metal wires are used to create the clocking field [26]. Bernstein, *et al* are investigating mechanisms for detecting the output of QCA circuits. The output of the metal-dot systems were detected using single electron transistor electrometers [8] [36].

Current estimates place fabrication of simple molecular circuits being possible within three to five years. More complex circuits and large scale fabrication will require more time, but are expected to be possible before the end of the roadmap is reached and nanoscale devices are required to meet density, speed, power and performance demands.

## 1.6 Introduction to the H Memory

This thesis presents a memory framework for QCA and several enhancements on the design. Some architectural work has been done designing memory [9] and processors [4]. However, this is the first effort in designing "native" QCA storage structures. Because of this, the proposed architecture is a departure from traditional SRAM and DRAM designs. These designs can be implemented in QCA, but the resulting designs are awkward and inefficient, providing only minimal gains over CMOS. The goal, then, was to design a highly dense memory native to QCA - to take advantage of properties of QCA in ways that today's memory designs take advantage of the properties of CMOS. The basic tool chest, as mentioned above, contains the majority gate, the inverter, the inherent latching and pipelining in QCA wires, the connection

between layout and timing, and finally the constant motion of data.

The design that these tools lent themselves to is a serially accessed structure based on a binary tree arranged in a recursive H structure (figure 1.8). Memory macros store a word of data and contain the logic necessary to satisfy read and write requests. Router macros send memory requests toward the appropriate memory macro. In essence, accessing data becomes a routing problem. Data is stored at

Figure 1.8. Basic H-memory Layout showing the organization of memory macros labeled "mem" and router macros labeled "rtr". Accesses enter at the root on the right and travel through the internal router macros to a memory macro leaf, then back through the router macros to the root to exit the memory.

the leaves of the H-tree, and internal nodes are routers. In the basic framework, all memory accesses originate at the root of the memory and consist of two parcels of bits that travel on two parallel lines in lockstep with each other. One parcel contains the address, write enable, and data word. The other is responsible for signaling the presence of meaningful bits to the routers and leaves. This routing approach to accesses is natural to QCA and offers interesting architectural opportunities. In particular, it allows a simple way to incorporate logic into the memory structure itself. Performing simple ALU functions in the routers or leaves can alleviate the von Neumann bottleneck, and fully incorporating the logic of the processing unit into the memory eliminates the von Neumann bottleneck altogether by eliminating the "central" of the central processing unit.

## 1.7 Original Contributions

My original contribution to this thesis includes the H-memory access method; the design, implementation, and analysis of the data loops and H-memory; the leaf enhancement design and analysis; the collision and execution time analyses for the bouncing threads enhancement; the simulator that allowed the exploration of the bouncing threads model in the presence of collisions; and finally, the discussion and analysis of the diagonal clocking wire layout.

# 1.8 Thesis Map

This chapter introduced the problem addressed here and the basics of the QCA device. Chapter 2 will discuss current storage structures including the different types of memories, silicon friendly architectures, and non-conventional memories. Chapter 3 will discuss the H-memory architecture. Chapter 4 will discuss a first cut implementation and its predicted performance. Chapter 5 will discuss two enhancements to the basic memory structure. The first is storing multiple words in each memory macro. The second is incorporating logic into the memory structure. Chapter 6 discusses an alternate clocking wire layout strategy and the corresponding effects on architecture. Finally, chapter 7 concludes and discusses some future work.

# CHAPTER 2

## Today's Memories

Traditional computer architecture has split its focus between logic and memory. Logic is responsible for computation, and memory is responsible for storing the state necessary for the desired computation. This state includes data with a wide range of persistence times, from short term data placed in buffers to permanent configuration information stored at fabrication time. Today's memories are based on arrays of memory cells. There are two main characteristics on which to classify these memories: volatility and access method. A third important classification subdivides the access method into storage method, either static or dynamic (figure 2.1). The latter half of this chapter discusses a few emerging nanotechnology proposals that may challenge contemporary commercial memories in the future.

The first axis on which to classify is volatility. Memory can be either volatile or non-volatile. Volatile memory is usually used for data that changes frequently such as main memory contents and usually allows fast read and write times. However, it needs to be connected to a power source and may need to be refreshed periodically. Non-volatile memory retains its data even after being removed from its power source. Hard drives and flash memory sticks are common examples of non-volatile memory.

The second axis on which to classify memories is the access method, consisting of read-only memory, random access memory, and content-addressable memory. Read-only memory (ROM) or read-mostly memory is generally non-volatile and

|                     | Volatile |        | Non-Volatile             |

|---------------------|----------|--------|--------------------------|

|                     | Dynamic  | Static |                          |

| Random Access       | DRAM     | SRAM   | FeRAM                    |

| Content Addressable |          | САМ    |                          |

| Read Only           |          |        | EPROM<br>EEPROM<br>Flash |

Figure 2.1. Memory Type Classification

used for data that is expected not to change, or to change rarely in the case of readmostly memory. Random access memory (RAM) is a read/write memory, generally volatile, and used for data that changes often. Content-addressable memory (CAM), or associative memory, is a random access, read/write memory that allows access by data rather than by address. RAMs are presented an address and return the data associated with that address. CAMs are presented a data word and return the address with which that data is associated. RAM can be further subdivided into dynamic versus static storage. Dynamic RAM (DRAM) stores its data on a capacitor and requires a periodic refresh. Static RAM (SRAM) stores its data in a latch and avoids the need for a refresh.

The ideal memory would combine non-volatility, fast read times and fast write times. However, these three goals are often directly conflicting. For instance, nonvolatility requires that data be hard to erase. Fast write times, on the other hand, require easily erased materials. Often times, easily writable materials lead to difficult to read materials since the read process must be very gentle relative to the write process. For the present, non-volatility is generally joined with read oriented applications, and volatility is tolerated by write oriented applications.

## 2.1 Array Memory

Each type of memory has a unique memory cell that does the actual bit storage, but most of these memories share a basic array architecture. The magnetic, optical and holographic disks are the exceptions. Memory cells are placed at the intersections of vertical and horizontal wires, or columns and rows. They are also known as wordlines and bit-lines, respectively. A bit is accessed when both its wordline and bitline are activated. In figure 2.2, a standard dynamic random access memory architecture is shown. The memory itself will be discussed below, but the architecture contains all the pieces common between the array memories. A particular bit in the array of bits, or cell matrix, is identified by an address. In the example, there are 10 address bits. Five bits identify the desired column (C1..C5), and five bits identify the desired row (R1..R5). Decoders on the column and row inputs translate the five bit partial addresses into one of 32 wires. When the address is presented to the address input buffers, the one bit data word at the intersection of the active row and column is selected to be operated upon (either read or written). This is a very simple example of an array architecture. Modern array memories contain multiple banks that allow larger data words to be used and to support faster data access.

# 2.2 Volatile Random Access Memory

Random access memories are generally volatile. This is generally appropriate since randomly accessed data tends to change often, requiring a quick and efficient write process. For instance, main memory and caches in general purpose computers commonly use dynamic RAM (DRAM) and static RAM (SRAM). DRAM is used where high density or low cost is important. SRAM is generally used where high speed is

Figure 2.2. Basic array architecture for 1024x1 configuration, 10 address bits [30]

necessary.

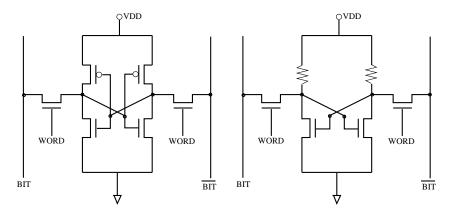

Figure 2.3. (a) 6 Transistor SRAM cell. (b) 4 Transistor SRAM cell

The static and dynamic options for memory cells generally trade off speed and area (figure 2.5). Static RAM (SRAM) stores data on latches and maintains its value as long as the power is on. Dynamic RAM (DRAM) stores the bit on a capacitor and requires the value to be refreshed periodically (figure 2.4). DRAM cells have a

Figure 2.4. A one transistor, one capacitor DRAM cell

Figure 2.5. Density projections for SRAM and DRAM [28]

typical retention rate of 64 ms [28].

SRAM cells consist of a standard cross-coupled inverter latch and two additional transistors to control access to the data. The latch can be implemented either in CMOS with six transistors or in pseudo-NMOS with four transistors (figure 2.3). SRAM is between eight and sixteen times faster than DRAM since it does not lose time for data refreshing and for recovering from destructive reads. However, the SRAM cell requires four to eight times more area than the DRAM cell.