Computer Architecture I

CSE 30321

356a Fitzpatrick Hall

Tuesday/Thursday, 11:00 a.m. - 12:15 p.m.

Course Objectives

To provide a thorough introduction to the architectural features of present-day serial, scalar machines. To instill in students basic knowledge of assembly language programming. To provide first experience in designing and evaluating architecture v.s. organization v.s. ximplementation of computer systems using commercial computer-aided design software.

Midterm Exam Grades

Course Schedule

| Date | Day | Topic | Suggested Reading | Assignments | ||||

|---|---|---|---|---|---|---|---|---|

| 1 | Aug. 26 | T | Course Introduction, Technology Review, Logistics (pdf) | Vahid, Chapter 8 | ||||

| 2 | Aug. 28 | H | Programmable Processors + 3 Instruction Processor (pdf)(ppt) | |||||

| 3 | Sep. 2 | T | 3 Instruction Processor + 6 Instruction Processor -- Updated Slides (pdf) | HW1 Out (pdf) HW1 Solutions (pdf) (3 person groups allowed) |

||||

| Review: Verilog and Finite State Machines (8:15 pm in 356a) (pdf of notes) | ||||||||

| 4 | Sep. 4 | H | The 6 Instruction Processor (Continue with Lec. 02/03 slides) | |||||

| 5 | Sep. 9 | T | Architectural Performance Metrics (Slides pdf) | Patterson Chapter 1 | HW1 Due HW2 Out (pdf) HW2 Solutions (pdf) (Datapath) (FSM) (3 person groups allowed) |

|||

| Review: Performance Metrics (8:15 pm in 356a) (pdf of notes) | ||||||||

| 6 | Sep. 11 | H | Performance Metrics + The MIPS ISA (MIPS Slides pdf) | Patterson Chapter 2 | ||||

| 7 | Sep. 16 | T | MIPS Assembly (MIPS Slides pdf) | HW2 Due HW3 Out (pdf) HW3 Solutions (pdf) (3 person groups allowed) |

||||

| 8 | Sep. 18 | H | MIPS Assembly Examples + MIPS Procedure Calls (slides pdf) | |||||

| 9 | Sep. 23 | T | MIPS Procedure Calls (slides pdf) | HW3 Due HW4 Out (pdf) HW4 Solutions (pdf) (3 person groups allowed) |

||||

| 10 | Sep. 25 | H | MIPS Procedure Call Examples + MIPS ISA Wrap-up (see notes from Lecture 09) | |||||

| Sep. 26 | F | Lab 03 Released | ||||||

| 11 | Sep. 30 | T | Single Cycle Processor Design (slides pdf) (slides ppt) | HW4 Due HW5 Out (pdf) HW5 Solutions (pdf) (3 person groups allowed) |

||||

| Oct. 1 | W | Lab 03 Assigned | ||||||

| 12 | Oct. 2 | H | Single Cycle Processor Design | |||||

| Oct. 6 | Evening office hours (5:00 - 7:00 pm) | |||||||

| 13 | Oct. 7 | T | Single Cycle Processor Design | HW5 Due | ||||

| Evening office hours (5:30 - 7:00 pm) | ||||||||

| Oct. 8 | W | Lab 04 Assigned, Lab 03 Due | ||||||

| 14 | Oct. 9 | H | Single Cycle Processor Design | |||||

| Oct. 11 | Midterm Review Session Last Year's Midterm (pdf) Solutions (pdf) |

|||||||

| 15 | Oct. 14 | T | In Class Midterm | |||||

| Oct. 15 | W | Lab 04 Due | ||||||

| 16 | Oct. 16 | H | Introduction to Multicycle Processors | |||||

| Oct. 21 | T | No Class: Fall Break! | ||||||

| Oct. 23 | H | No Class: Fall Break! | ||||||

| 17 | Oct. 28 | T |

Review + Development of a Multicycle Processor

Course Goal Review (pdf) Multicycle Slides (pdf) Multicore Slides (pdf) |

Lab 04 due at cost of one late day HW6 Out (pdf) HW6 Figures (pdf) |

||||

| 18 | Oct. 30 | H | Development of a Multicycle Processor (pdf) | |||||

| 19 | Nov. 4 | T |

Exceptions/Control Logic in Multicycle Processors (pdf) Introduction to Pipelining (pdf) |

HW6 Due HW6 Solutions (pdf) HW7 Out Problem 1-5(pdf) Problem 6(pdf) |

||||

| Nov. 5 | W | Lab 06 Assigned, Lab 05 Due | ||||||

| 20 | Nov. 6 | H | Pipelining Hazards (pdf) | |||||

| 21 | Nov. 11 | T | Pipelined Processors (pdf) | HW7 Due Final Projcect Out |

||||

| 22 | Nov. 13 | H | Introduction to Caches (pdf)(pdf) | |||||

| Extra office hours to discuss projects. | ||||||||

| 23 | Nov. 18 | T | More Caches (pdf) Extra Problem Solutions |

Final Project Proposal Due HW8 Out Problems 1-5(pdf) Problem 6(pdf) Solutions 1 (pdf) Solutions 2 (pdf) |

||||

| Nov. 19 | W | Lab 06 Due | ||||||

| 24 | Nov. 20 | H | Cache wrap-up + Virtual Memory (pdf) | |||||

| 25 | Nov. 25 | T | Virtual Memory Extra Problem Solutions Chris Fallin's Notes |

HW8 Due Final Project Progress Report Due |

||||

| Nov. 27 | H | No Class: Happy Thanksgiving! | ||||||

| 26 | Dec. 2 | T | Storage and I/O (pdf) Example (pdf) | HW 9 Out (pdf) Solutions (pdf) |

||||

| 27 | Dec. 4 | H | Storage and I/O (pdf) | |||||

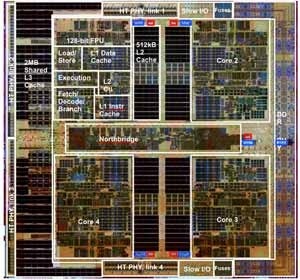

| 28 | Dec. 9 | T | Multi-core Architectures (pdf) (pdf) | |||||

| 29 | Dec. 11 | H | Review | |||||

| H | Final: Thursday, December 18th, 10:30-12:30 | |||||||

Lab Resources

Lab resources and handouts can be found here.

Required Texts

- David A. Patterson and John L. Hennessy, Computer Organization and Design: The Hardware/Software Interface, 3rd Edition, Morgan Kaufmann Publishers, 2005.

- Frank Vahid, Digital Design, John Wiley & Sons, Inc., 2007.

Contact Information

Instructor

-

Michael T. Niemier(mniemier@nd.edu)

380 Fitzpatrick Hall

Notre Dame, IN 46556

(574) 631-3858

Office Hours: Thursday 3:30-5:00 p.m., Friday 8:30-10:00 a.m.

Graduate TAs

-

Aaron Dingler (labs) (afs id = adingler)

Office Hours: Monday, Wednesday 12:30 - 1:30 p.m.

Veena Thomas (HWs) (afs id = vthomas2)

Office Hours: Monday 12:00 - 1:30 p.m.

Undergraduate TAs

-

Chris Fallin (labs and HWs) (afs id = cfallin)

Office Hours: Monday, 3-4:30 pm in 208 Cushing

Nick Lovell (labs and HWs) (afs id = nlovell)

Office Hours: Tuesday, 2-3 pm in 208 Cushing