Course

Schedule |

|

Date |

Day |

Topic |

Suggested Reading |

Assignments |

| 1 |

Jan. 19 |

W |

Introduction and Course Overview

|

|

|

| 2 |

Jan. 24 |

M |

Review of FET-based computation + 5 "tenets" of

digital logic

|

|

|

| 3 |

Jan. 26 |

W |

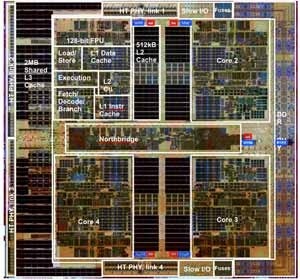

Review of FET-based computation + state of the art

(Intel perspective)

|

-

ITRS Roadmap (ITRS)

-

"Reducing Variation in Advanced Logic Technologies: Approaches

to Process and Design for Manufacturability of Nanoscale CMOS" (DOI)

-

"High-performance CMOS variability in the 65-nm regime and beyond" (DOI)

-

"Digital Circuit Design Challenges and Opportunities in the

Era of Nanoscale CMOS" (DOI)

-

"Adaptive circuits for the 0.5-V nanoscale CMOS era" (DOI)

-

"Power-constrained CMOS scaling limits" (DOI)

|

|

| 4 |

Jan. 31 |

M |

Interconnect Scaling

|

|

|

| 5 |

Feb. 7 |

M |

Fundamental Limits of Computation

|

|

|

| 6 |

Feb. 9 |

W |

3D Integration

|

|

|

| 7 |

Feb. 14 |

M |

Carbon nanotube electronics

|

-

CNT Background: Performance Analysis of Carbon

Nanotube Interconnects for VLSI Applications, Navin

Srivastava and Kaustav Banerjee, ICCAD 2005.

-

CNT Interconnect: Carbon

Nanotube Interconnects: Implications for Performance, Power

Dissipation and Thermal Management, Navin Srivastava,

Rajiv V. Joshi, and Kaustav Banerjee, IEDM 2005.

-

CNT Interconnect:

Are Carbon Nanotubes the Future of VLSI

Interconnections?, Kaustav Banerjee and Navin

Srivastava, DAC 2006.

-

CNT FETs: In

Search of Forever, Continued Transistor Scaling One New

Material at a Time, Scott E. Thompson,

Robert S. Chau, Tahir Ghani, Kaizad Mistry, Sunit Tyagi,

and Mark T. Bohr, IEEE T. on Semiconductor Manufacturing.

-

CNT FETs ACCNT

– A Metallic-CNT-Tolerant Design Methodology for Carbon-Nanotube

VLSI: Concepts and Experimental Demonstration, Albert

Lin, Nishant Patil, Hai Wei, Subhasish Mitra, and H.-S. Philip

Wong, IEEE Transactions on Electron Devices.

-

Graphene Graphene

Electronics, Unzipped, Alexander Sinitskii and James

Tour, IEEE Spectrum.

|

|

| 8 |

Feb. 16 |

W |

FinFETs

|

-

Turning Silicon on Its Edge, Edward

J. Nowak, et al, IEEE Circuits and Devices Magazine, January/February 2004, p. 20-31.

-

Integrated

CMOS Tri-Gate Transistors: Paving the Way to Future

Technology Generations, Robert S. Chau,

Technology@Intel Magazine, August 2006, p. 1-7.

-

In Search of “Forever,” Continued Transistor

Scaling One New Material at a Time, Scott E. Thompson, et al, IEEE T. on Semiconductor Manufacturing.

-

Transistors

Go Vertical, Sarah Adee, IEEE Spectrum.

-

Simulation

Study of Multiple FIN FinFET Design for 32 nm Technology

Node and Beyond, Xinlin Wang, et al, Simulation of Semiconductor Processes and Devices, Volume 12, p. 125-128, 2007.

-

Evaluation

of Multiple Supply and Threshold Voltages for Low-Power FinFET

Circuit Synthesis,

Prateek Mishra, Anish Muttreja, and Niraj Jha, IEEE International Symposium on Nanoscale Architectures, p. 77-84, 2008.

|

|

| 9 |

Feb. 21 |

M |

Tunnel Transistors (TFETs)

|

-

On Enhanced Miller Capacitance Effect in Interband Tunnel Transistors, Saurabh Mookerjea, Ramakrishnan Krishnan, Suman Datta, and Vijaykrishnan Narayanan, IEEE Electron Device Letters, 30(10), p. 1102-1104, October, 2009.

-

Low Power Circuit Design Based on Heterojunction Tunneling Transistors (HETTs), Daeyeon Kim, Yoonmyung Lee, Jin Cai, Isaac Lauer, Leland Chang, Steven J. Koester, Dennis Sylvester, David Blaauw , ISLPED, August 19th-21st, 2009.

-

A Novel Si-Tunnel FET based SRAM Design for Ultra-Low Power 0.3 V VDD Applications, J. Singh, K. Ramakrishnan, S. Mookerjea, S. Datta‡, N. Vijaykrishnan, D. Pradhan, ASP-DAC, January 18-21, 2010, p. 181-186.

-

Compound Semiconductor Based Tunnel Transistor Logic, Suman Datta, S. Mookerjea, D. Mohata, L. Liu, V. Saripalli, V. Narayanan and T. Mayer, CSManTech Conference.

-

Low-Voltage Tunnel Transistors for Beyond CMOS Logic, Alan Seabaugh and Qin Zhang, Proceedings of the IEEE, 98(12), p. 2095-2010, December, 2010.

-

It’s Time to Reinvent the Transistor, Thomas N. Theis and Paul M. Solomon, Science, Volume 327, p. 1600-1601, March 26, 2010.

|

|

| 10 |

Feb. 23 |

M |

Low Voltage MOSFETs

|

-

Energy Optimization of Subthreshold-Voltage

Sensor Network Processors, L. Nazhandali, B. Zhai, J. Olson,

A. Reeves, M. Minuth, R. Helfand, S. Pant, T. Austin, and

D. Blauuw, Proceedings of the 32nd International Symposium on

Computer Architecture.

-

Serial

Subthreshold Circuits for Ultra-Low Power Systems,

Sudhanshu Khanna and Benton H. Calhoun, Proceedings of ISLPED, 2009.

-

Probabilistic Arithmetic and Energy Efficient

Embedded Signal Processing, J. George, B. Marr,

B. E. S. Akgul, and K. V. Palem, Proceedings of Computer

Architecture Support for Embedded Systems (CASES), October 23-25, 2006, Seoul, Korea.

-

Advocating Noise

as an Agent for Ultra-Low Energy Computing:

Probabilistic Complementary Metal–Oxide–Semiconductor

Devices and Their Characteristics,

Pinar Korkmaz, Bilge E. S. Akgul, Krishna V. Palem, and

Lakshmi N. Chakrapani,

Japanese Journal of Applied Physics, Vol. 45, No. 4B, 2006, pp. 3307–3316.

|

|

| 11 |

Feb. 28 |

M |

Probabilistic CMOS + NEMS Relays

|

-

Integrated

Circuit Design with NEM Relays,

Fred Chen, Hei Kam, Dejan Markovic, Tsu-Jae King Liu,

Vladimir Stojanovic, Elad Alon,

Proceedings of International Conference on Computer Aided Design, San Jose, CA, p. 750-757, November 10-13, 2008.

-

Demonstration

of Integrated Micro-Electro- Mechanical Relay Circuits for VLSI

Applications, Matthew Spencer, Fred Chen, Cheng C. Wang,

Rhesa Nathanael, Hossein Fariborzi, Abhinav Gupta, Hei Kam,

Vincent Pott, Jaeseok Jeon, Tsu-Jae King Liu, Dejan Markovic ́,

Elad Alon, and Vladimir Stojanovic , IEEE Journal of

Solid-State Circuits, 46(1), p. 308-320.

-

Mechanical

Computing Redux Relays for Integrated Circuit

Applications, Vincent Pott, Hei Kam,

Rhesa Nathanael, Jaeseok Jeon, Elad Alon, and Tsu-Jae King Liu, Proceedings of the IEEE, 98(12), p. 2076-2094, December, 2010.

|

|

| 12 |

Mar. 2 |

W |

Reliable Computation, Unreliable Components

|

|

|

| 13 |

Mar. 7 |

M |

NW Crossbar Architectures

|

-

Directed Assembly of One-Dimensional Nanostructures into Functional Networks, Lieber, et al., Science, Vol. 291, January 26, 2001.

-

Logic Gates and Computation from Assembled Nanowire Building Blocks, Lieber, et al., Science, Vol. 294, November 9, 2001.

-

Nanowire-Based Programmable Architectures, Andre Dehon, ACM Journal on Emerging Technologies, Vol. 1(2), July 2005, p. 109-162.

-

Nanowire-Based Sublithographic Programmable Logic Arrays, Andre Dehon and Michael Wilson, FPGA Conference, February 22-24, 2004.

|

|

| 14 |

Mar. 9 |

W |

NW Crossbar Architectures

|

-

Directed Assembly of One-Dimensional Nanostructures into Functional Networks, Lieber, et al., Science, Vol. 291, January 26, 2001.

-

Logic Gates and Computation from Assembled Nanowire Building Blocks, Lieber, et al., Science, Vol. 294, November 9, 2001.

-

Nanowire-Based Programmable Architectures, Andre Dehon, ACM Journal on Emerging Technologies, Vol. 1(2), July 2005, p. 109-162.

-

Nanowire-Based Sublithographic Programmable Logic Arrays, Andre Dehon and Michael Wilson, FPGA Conference, February 22-24, 2004.

|

|

|

Mar. 14 |

M |

No Class: Spring Break |

|

Mar. 16 |

W |

No Class: Spring Break |

| 15 |

Mar. 21 |

M |

CMOL and FPNI

|

-

CMOL FPGA: a reconfigurable architecture for hybrid digital circuits with two-terminal nanodevices, Strukov and Likharev, Nanotechnology 16, p. 888-900.

-

Prospects for terabit-scale nanoelectronic

memories, Strukov and Likharev, Nanotechnology 16, p. 137-148, 2005.

-

CMOL: Devices, Circuits, and Architectures, Strukov and Likharev, 2004.

-

Nano/CMOS architectures using a field-programmable nanowire interconnect, Snider and Williams, Nanotechnology, 18, 035204, 2007.

|

|

| 16 |

Mar. 23 |

W |

Analog Neural Networks

|

|

|

| 17 |

Mar. 28 |

M |

Analog Neural Networks

|

-

Self-organized computation with unreliable, memristive nanodevices, Greg Snider, Nanotechnology, 18, 365202, 2007.

-

The Cat is Out of the Bag: Cortical Simulations with 10^9 Neurons, 10^13 Synapses, Ananthanarayanan, et al., Supercomputing, November 14-20, 2009.

|

|

| 18 |

Mar. 30 |

W |

Introduction to MRAM

|

-

The

Discoery of Giant Magnetoresistance, compiled by the Class

for Physics of the Royal Swedish Academy of Sciences, The

Royal Sweedish Academy of Sciences (2007).

-

Toward

a Universal Memory, Johan Åkerman, Science, Vol 308, 2005.

-

The

Promise of Nanomagnetics and Spintronics for Future Logic and

Universal Memory, S. Wolf, et al., Proc. of the IEEE, 2010.

|

|

| 19 |

Apr. 6 |

W |

Nanomagnet Logic

|

-

See instructor for pre-prints if desired.

|

|

| 20 |

Apr. 11 |

M |

Spin Wave Buses

|

-

Nano

scale computational architectures with Spin Wave

Bus, Alexander Khitun and Kang L. Wang, Superlattices and Microstructures 38 (2005) 184–200.

-

Spin

Wave Magnetic NanoFabric: A New Approach to Spin-Based

Logic Circuitry, Alexander Khitun, Mingqiang Bao, and

Kang L. Wang, IEEE T. on Magnetics, Vol. 44, No. 9, September, 2008.

|

|

| 21 |

Apr. 13 |

W |

MTJ-based logic

|

-

The

Promise of Nanomagnetics and Spintronics for Future Logic and

Universal Memory, S. Wolf, et al., Proc. of the IEEE, 2010.

-

Fabrication of

a Nonvolatile Full Adder Based on Logic-in-Memory Architecture

Using Magnetic Tunnel Junctions, Matsunaga, et al.,

Applied Physics Express 1(2008) 091301.

-

MTJ-Based Nonvolatile Logic-in-Memory Circuit,

Future Prospects and Issues , Matsunaga, et al., Proceedings

of DATE (2009).

-

True Energy-Performance Analysis of the

MTJ-Based Logic-in-Memory Architecture (1-Bit Full Adder),

Fengbo Ren and D. Markovic, IEEE T. on Electron Devices,

57(5), p. 1023-1028, 2010.

-

Proposal of a spin torque majority gate logic , Dmitri E. Nikonov, George I. Bourianoff, and Tahir Ghani.

|

|

| 22 |

Apr. 18 |

M |

RAMA and All Spin Logic

|

-

The

Promise of Nanomagnetics and Spintronics for Future Logic and

Universal Memory, S. Wolf, et al., Proc. of the IEEE, 2010.

-

Proposal

for an all-spin logic device with built-in memory,

Behin-Aein, et al., Nature Nanotechnology.

-

Switching

energy-delay of all spin logic devices, Behin-Aein, et al.,

Applied Physics Letters.

-

2

Mb SPRAM (SPin-Transfer Torque RAM) With Bit-by-Bit

Bi-Directional Current Write and Parallelizing-Direction Current

Read, T. Kawahara, et al., IEEE Journal of Solid State Circuits.

|

|

| 23 |

Apr. 20 |

W |

Memory Benchmarks + Flash

|

-

The

Promise of Nanomagnetics and Spintronics for Future Logic and

Universal Memory, S. Wolf, et al., Proc. of the IEEE, 2010.

-

2

Mb SPRAM (SPin-Transfer Torque RAM) With Bit-by-Bit

Bi-Directional Current Write and Parallelizing-Direction Current

Read, T. Kawahara, et al., IEEE Journal of Solid State Circuits.

-

Advances

and Future Prospects of Spin-Transfer Torque Random Access

Memory, E. Chen, et al., IEEE T. on Magnetics.

|

|

|

Apr. 25 |

M |

No Class: Easter Break |

| 24 |

Apr. 27 |

W |

STT-RAM, PCM, & Racetrack Memories

|

-

The

Promise of Nanomagnetics and Spintronics for Future Logic and

Universal Memory, S. Wolf, et al., Proc. of the IEEE, 2010.

-

2

Mb SPRAM (SPin-Transfer Torque RAM) With Bit-by-Bit

Bi-Directional Current Write and Parallelizing-Direction Current

Read, T. Kawahara, et al., IEEE Journal of Solid State Circuits.

-

Advances

and Future Prospects of Spin-Transfer Torque Random Access

Memory, E. Chen, et al., IEEE T. on Magnetics.

|

|

| 25 |

May 2 |

M |

Impact of NV memory on architecture

|

|

|

| 26 |

May 4 |

W |

Optical Interconnect

|

|

|

|

May 11 |

|

Final

project report due on 5/11 |

|